L’intelligence artificielle vient de franchir une étape majeure dans l’un des domaines les plus complexes de l’ingénierie : la conception de semi-conducteurs. La startup Verkor.io affirme que son système Design Conductor a été capable de créer de manière autonome un cœur de CPU RISC-V complet, appelé VerCore, à partir d’un document de spécifications de seulement 219 mots et en seulement 12 heures.

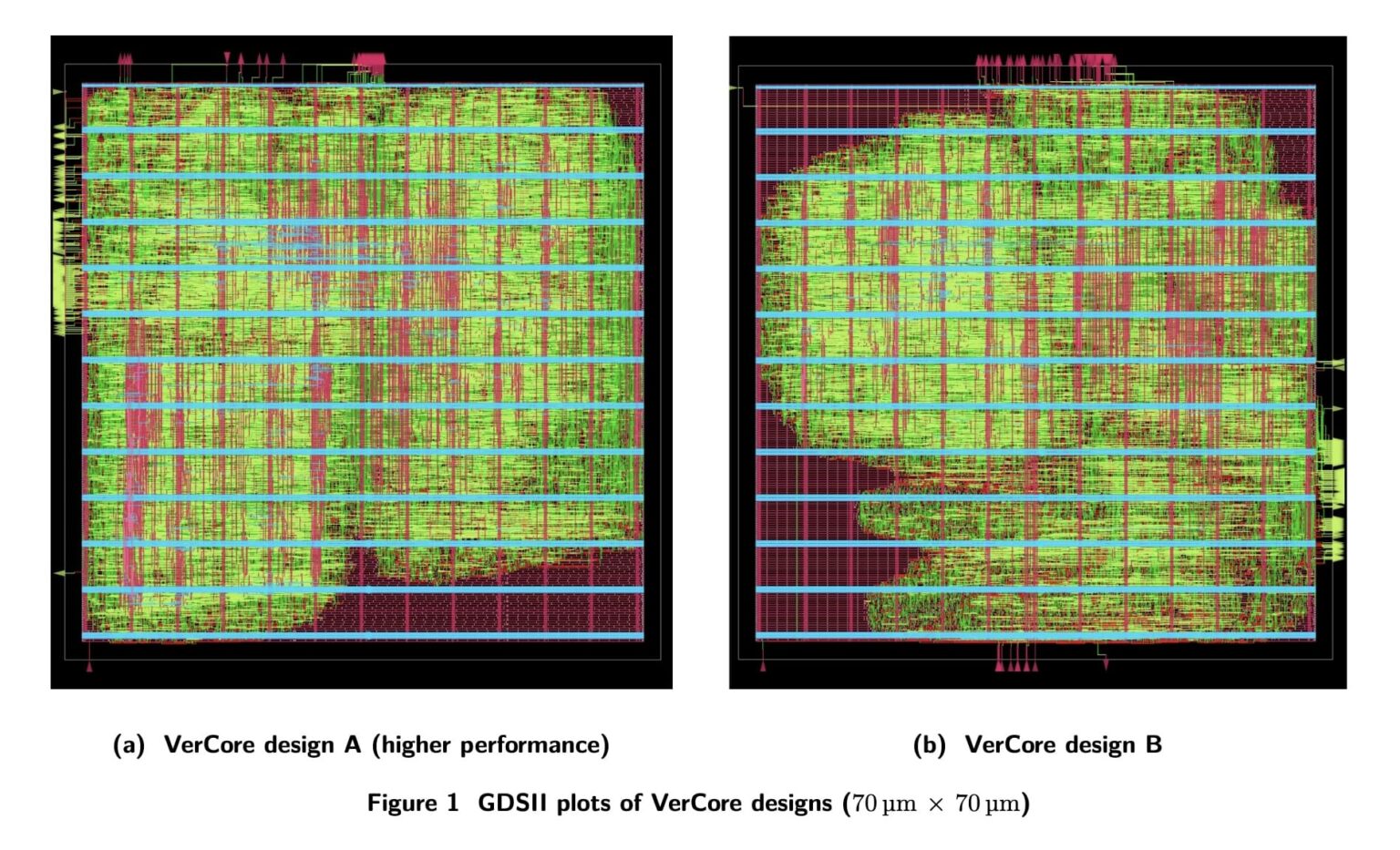

Cette déclaration est impressionnante, mais il convient de l’analyser avec précision. Il ne s’agit pas qu’un modèle de langage ait fabriqué physiquement un processeur ni qu’il ait conçu une CPU comparable aux chips modernes d’Intel, AMD, Apple ou Arm. Ce que Verkor.io soutient, c’est que son agent d’IA a parcouru l’intégralité du flux de conception numérique, du cahier des charges initial jusqu’à un fichier GDSII, le format de layout utilisé lors des phases finales avant la fabrication d’un circuit intégré.

Un processeur simple, mais conçu de bout en bout

VerCore se présente comme un noyau RISC-V compatible RV32I et ZMMUL, avec une architecture simple à cinq étages, un ordre d’exécution en pipeline et une émission d’une seule instruction par cycle. Selon le document technique publié par Verkor.io, la conception a atteint une fréquence de 1,48 GHz en utilisant ASAP7, une plateforme académique de simulation de processus en 7 nm, et a obtenu 3 261 en CoreMark, un benchmark courant pour mesurer la performance de microcontrôleurs et CPU embarqués.

Le rapport compare également ce résultat à celui d’un Intel Celeron SU2300 de 2011, un processeur modeste même pour l’époque. Cette comparaison permet de contextualiser l’avancée : VerCore n’est pas destiné à concurrencer les processeurs actuels ni à le faire un jour. Son intérêt réside dans le processus, pas nécessairement dans la puissance finale du chip.

Design Conductor n’est pas un modèle d’IA isolé, mais plutôt un outil d’orchestration qui guide des modèles avancés dans l’exécution de tâches de conception, de revue, de débogage et d’optimisation. Dans ce cas précis, le système a reçu une spécification concise demandant une CPU RISC-V avec interface de cache d’instructions, interface de cache de données, conception pipeline à cinq étages, support RV32I et ZMMUL, absence d’instructions comprimées, et un objectif CPI inférieur ou égal à 1,5.

À partir de là, l’agent a généré des propositions microarchitecturales, implémenté des modules en Verilog, créé des bancs d’essai, comparé le comportement du processeur avec Spike — le simulateur de référence RISC-V —, corrigé des erreurs fonctionnelles, et ajusté le design physique via des outils d’automatisation de la conception électronique.

L’importance du GDSII et la nuance cruciale : il n’a pas encore été fabriqué

L’étape vers le GDSII est importante car ce fichier représente le layout physique du chip, une description prête pour les phases finales de fabrication. Dans la conception traditionnelle de semi-conducteurs, cette étape requiert des architectes, des ingénieurs RTL, des spécialistes en vérification, des experts en timing, des équipes de backend et un flux complexe d’outils EDA.

Le document de Verkor.io rappelle qu’un développement de puce de pointe peut coûter plus de 400 millions de dollars et durer de 18 à 36 mois, avec des équipes de centaines d’ingénieurs. Dans ce contexte, le fait qu’un agent ait pu produire un design fonctionnel et vérifiable en simulation en 12 heures est remarquable, même si le modèle de CPU reste relativement simple.

La principale prudence est que VerCore n’a pas encore été fabriqué. Le design a été validé en simulation et reproduit sous ASAP7, un PDK académique développé par l’Université d’État de l’Arizona en collaboration avec ARM Research. Cela signifie que le résultat n’est pas un vrai chip commercial prêt pour la production, mais une démonstration technique d’un flux de conception automatisé.

Il faut aussi considérer que la vérification d’un vrai circuit pour une production de masse est beaucoup plus exigeante que les tests fonctionnels et benchmarks en simulation. En semi-conducteurs, une erreur découverte après le tape-out peut entraîner des coûts très élevés. C’est pourquoi la vérification représente souvent une part importante du processus de développement.

Ce que l’IA apporte à la conception de chips

La partie la plus innovante du travail de Verkor.io réside dans la façon dont l’agent semble avoir suivi une méthodologie similaire à celle d’une équipe humaine : concevoir, tester, repérer les erreurs, les corriger, puis réévaluer. Le rapport décrit comment Design Conductor a analysé des tracés VCD, converti des données de simulation en fichiers CSV, localisé des fautes de lecture dans des registres, et corrigé des problèmes dans la logique de vidage de pipeline après des sauts.

Le système a également exploré différentes variantes microarchitecturales. Selon le document, il a expérimenté avec des pénalisations de saut d’un et deux cycles, implémenté un forwarding précoce, et abouti à une solution utilisant un multiplicateur Booth-Wallace à quatre étages. Certaines décisions hybrides n’étaient pas indiquées dans la spécification initiale, laissant penser à une certaine capacité d’exploration technique dans un cadre à objectifs mesurables.

Cependant, le rapport lui-même reconnaît des limites importantes. Les modèles peuvent faire des raisonnements imparfaits avec Verilog, confondre parfois le comportement du hardware avec celui d’un programme séquentiel, et prendre des décisions sous-optimales avant de les corriger grâce à des rapports de timing. En clair : l’IA peut accélérer le processus, mais elle a encore besoin d’une supervision experte pour éviter de s’égarer.

RISC-V, un terrain d’expérimentation idéal

Le choix de RISC-V n’est pas anodin. Il s’agit d’une architecture ouverte et modulaire, maintenue par RISC-V International, qui est devenue un champ d’expérimentation très attractif pour la recherche, l’éducation, les microcontrôleurs, les designs personnalisés et les nouveaux processeurs spécialisés.

Sa nature ouverte facilite que des universités, start-up et entreprises puissent expérimenter avec de nouveaux noyaux sans les restrictions de licences que posent les architectures propriétaires. Associée à des outils open source comme OpenROAD et à des plateformes académiques telles qu’ASAP7, RISC-V constitue un terrain idéal pour explorer jusqu’où peut aller l’automatisation dans la conception hardware.

Le précédent de VerCore ne part pas de zéro. Ces dernières années, des expérimentations avec l’IA appliquée à la synthèse numérique, la génération de Verilog et la conception de circuits simples avaient déjà été réalisées. Ce qui est nouveau, selon Verkor.io, c’est d’avoir relié ces capacités dans un flux complet, allant de la spécification au layout GDSII d’une CPU fonctionnelle.

La prochaine étape sera de voir si d’autres ingénieurs peuvent reproduire le résultat. Verkor.io a indiqué qu’il prévoit de publier les fichiers de conception pertinents, permettant à des tiers de vérifier le RTL, les scripts et le flux de fabrication. Il prévoit également de présenter une implémentation FPGA de VerCore lors de la Design Automation Conference de Long Beach, prévue pour juillet.

En définitive, cette annonce ne doit pas être perçue comme la présentation d’une CPU révolutionnaire, mais comme une indication des directions possibles pour l’ingénierie des semi-conducteurs. Si ces systèmes évoluent, ils pourraient réduire le temps d’exploration, faciliter la création de variantes et aider de petites équipes à mener des projets aujourd’hui réservés à de grands groupes. Cependant, le passage d’une démonstration académique à une puce commerciale fiable reste encore très loin.

Questions fréquentes

Qu’est-ce que VerCore ?

VerCore est un noyau CPU RISC-V conçu par le système d’orchestration IA Design Conductor de Verkor.io. Il s’agit d’un processeur simple 32 bits, avec une architecture à cinq étages, exécution en pipeline et supportant RV32I et ZMMUL.

VerCore a-t-il déjà été fabriqué sous forme de puce physique ?

Non. Selon les informations disponibles, VerCore a été validé en simulation et reproduit dans un fichier GDSII, mais il n’a pas encore été fabriqué physiquement en tant que chip commercial ou prototype silice.

Que signifie qu’une IA ait abouti jusqu’au GDSII ?

Cela signifie que le système a généré un layout physique du circuit, une étape avancée de la conception de chips. Toutefois, atteindre le GDSII ne garantit pas que le chip soit prêt pour une production en masse, car il reste des validations et étapes industrielles à réaliser.

Une IA peut-elle remplacer les ingénieurs en conception de chips ?

Pas encore. Cet exemple montre que l’IA peut automatiser certaines parties de la conception et accélérer l’exploration de variantes, mais le rapport reconnaît également que la supervision d’ingénieurs et d’architectes demeure essentielle pour élaborer, vérifier et valider des designs complexes.