Intel et SoftBank, par le biais de SAIMEMORY, ont révélé de nouveaux détails sur HB3DM, une mémoire 3D basée sur Z-Angle Memory (ZAM) qui vise à devenir une alternative à la HBM traditionnelle pour les charges de travail en intelligence artificielle et en calcul haute performance. Il ne s’agit pas encore d’une mémoire commerciale prête à remplacer la HBM4 sur des accélérateurs de NVIDIA, AMD ou Intel, mais plutôt d’une proposition technique innovante dans un contexte où la bande passante mémoire est devenue l’un des principaux freins des infrastructures IA.

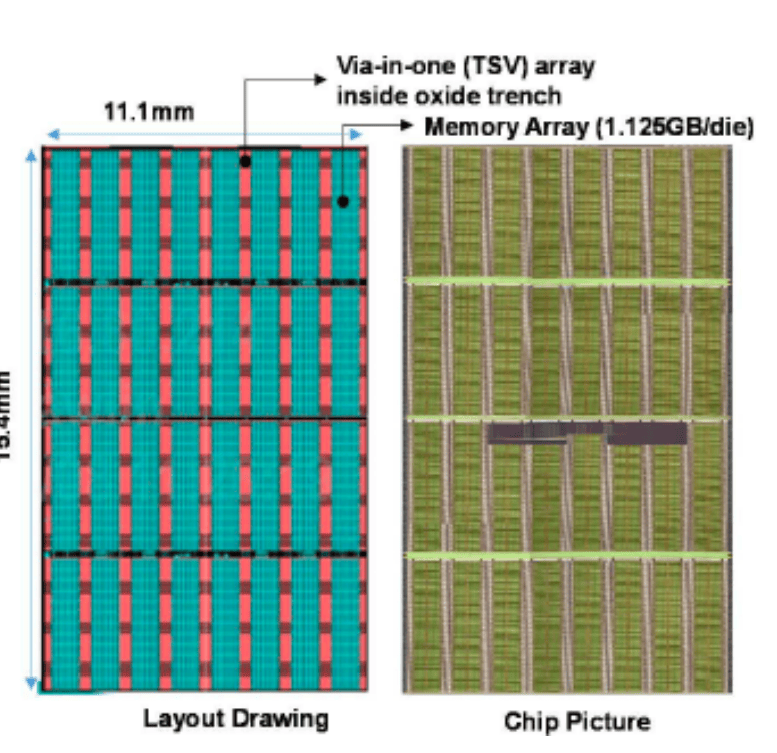

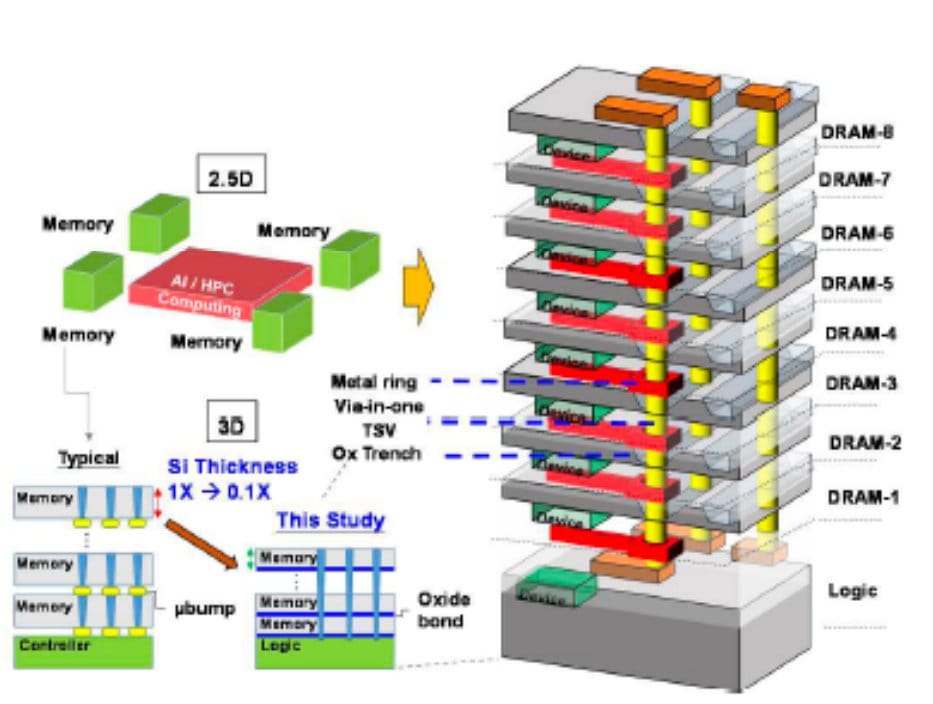

Les informations proviennent des données associées à une présentation prévue pour le VLSI Symposium 2026, qui se tiendra en juin à Honolulu. Selon les détails divulgués, la première démonstration de HB3DM utilise une empilement de neuf couches : une couche logique en base et huit couches de DRAM superposées, reliées par hybrid bonding, avec un substrat en silicium très fin, de seulement 3 µm par couche de DRAM.

Ce que propose HB3DM face à la HBM

La mémoire HBM actuelle repose déjà sur l’empilement de puces DRAM connectés verticalement via TSV, mais HB3DM cherche à pousser cette intégration vers un design encore plus dense. La couche logique inférieure gère le flux de données, tandis que les couches de DRAM stockent l’information. La promesse est claire : un débit supérieur par surface, une consommation réduite, et une architecture mieux adaptée aux accélérateurs d’intelligence artificielle.

SoftBank a annoncé en février que sa filiale SAIMEMORY avait signé un accord avec Intel pour faire progresser la commercialisation de Z-Angle Memory, une technologie de mémoire nouvelle génération conçue pour une haute capacité, un large débit et une faible consommation. La société vise à créer des prototypes pour l’exercice fiscal 2027 et espère lancer la commercialisation dès l’exercice fiscal 2029.

Les chiffres techniques connus pour HB3DM sont impressionnants. Chaque couche intégrerait environ 13 700 TSV, le die aurait une surface de 171 mm², et le débit total serait d’environ 0,25 Tb/s par mm². Sur cette surface, cela donne environ 5,3 TB/s par empilement. En capacité, la proposition tourne autour de 9 à 10 GB par module, bien en dessous des 36 ou 48 GB disponibles dans la HBM4 actuelle.

| Caractéristique | HB3DM/ZAM, selon les données diffusées |

|---|---|

| Structure | 1 couche logique + 8 couches de DRAM |

| Nombre total de couches | 9 |

| Épaisseur du substrat de DRAM | 3 µm par couche |

| Connexion verticale | Hybrid bonding |

| TSV par couche | Environ 13 700 |

| Capacité estimée | Autour de 9-10 GB par empilement |

| Surface du die | 171 mm² |

| Densité de bande passante | 0,25 Tb/s/mm² |

| Bande passante estimée | Environ 5,3 TB/s par empilement |

| Objectif de prototype | Exercice fiscal 2027 |

| Objectif commercial | Exercice fiscal 2029 |

Une comparaison avec la HBM4 doit être nuancée. Par exemple, Micron annonce une HBM4 avec interface de 2048 broches, des vitesses supérieures à 11 Gbps, et plus de 2,8 TB/s en configuration sur un seul empilement, avec des prototypes de 48 GB en configuration 16-high. HB3DM promet un débit supérieur, mais avec une capacité initiale inférieure. Pour les charges d’intelligence artificielle, ces deux variables sont cruciales : il ne suffit pas de faire transiter rapidement de grandes quantités de données si l’espace mémoire n’est pas suffisant à proximité du processeur.

Une architecture prometteuse, mais encore en développement

Intel et SAIMEMORY ne présentent pas une mémoire prête pour une production de masse. Leur feuille de route indique d’abord des prototypes, puis une commercialisation future. HB3DM en est encore au stade de validation technique, et ne constitue pas une alternative immédiate pour les accélérateurs attendus sur le marché en 2026 ou 2027.

Ce calendrier est important, car la HBM ne stagne pas non plus. SK hynix, Samsung et Micron travaillent déjà sur la HBM4 et la HBM4E, avec plus de capacité, une bande passante plus large, et des die de plus en plus sophistiqués. Lors de l’arrivée de ZAM à l’échelle commerciale, le marché pourrait déjà s’orienter vers la HBM5 ou des variantes spécifiques pour de grands clients.

Cependant, le concept reste pertinent. La demande en mémoire à très haut débit n’a fait que croître avec l’essor de l’intelligence artificielle. Modèles de langage, systèmes multimodaux, agents intelligents, et charges d’inférence ont besoin de déplacer d’énormes volumes de données avec une faible latence et une consommation maîtrisée. La pénurie et le coût de la HBM ont créé un espace favorable aux approches alternatives, même si aucun n’est encore totalement abouti.

Le rôle d’Intel est particulièrement intéressant. La société s’est éloignée depuis plusieurs années de la fabrication directe de mémoire, mais conserve un savoir-faire en empaquetage avancé, en interconnexion et en technologie d’empilement. SoftBank explique que SAIMEMORY tirera parti des technologies et de l’expérience validées par l’initiative Next Generation DRAM Bonding d’Intel, développée dans le cadre de programmes américains dédiés à la mémoire de nouvelle génération.

Cela ne signifie pas forcément qu’Intel produira directement ses propres couches mémoire traditionnelles. La production reste encore incertaine, tout comme la chaîne d’approvisionnement. TrendForce indique que l’on ignore encore quand SAIMEMORY commercialisera ses composants, ni qui fabriquera la DRAM de base, mais la participation d’Intel suggère qu’un retour indirect à la mémoire avancée pourrait se dessiner.

Plus de bande passante, moins de capacité

Le principal attrait de HB3DM réside dans sa largeur de bande. Un empilement pouvant atteindre environ 5,3 TB/s serait très compétitif pour certaines applications où le processeur doit accéder en continu à de grands flux de données. La densité par surface pourrait également permettre la conception d’accélérateurs plus compacts ou avec davantage de canaux mémoire dans le même espace d’emballage.

En revanche, la capacité constitue une limite. Un module d’environ 10 GB reste loin des chiffres actuels et futurs de la HBM4. Pour entraîner de grands modèles, la capacité et la bande passante doivent augmenter simultanément. Si un accélérateur doit utiliser plusieurs empilements HB3DM pour égaler la capacité d’une configuration HBM4, l’avantage en bande passante pourrait être contrebalancé par une complexité accrue, un coût plus élevé ou une consommation supérieure.

De ce fait, HB3DM ne doit pas être considéré uniquement comme une « alternative à la HBM ». Il pourrait s’intégrer dans des niches spécifiques : accélérateurs d’inférence, systèmes HPC spécialisés, architectures où le débit extrême prime, ou encore produits propres à Intel en cherchant à se différencier des stratégies de NVIDIA ou AMD.

Il faudra aussi surveiller l’efficacité thermique. Les stacks mémoire très denses rencontrent un frein physique évident : la dissipation thermique entre les couches. La technologie ZAM évoque une moindre consommation et une structure conçue pour améliorer la dissipation, mais il est encore difficile de mesurer dans des prototypes la véritable performance thermique en conditions réelles.

Une réduction de consommation jusqu’à 40 % par rapport à la HBM traditionnelle, évoquée dans les informations sur ZAM, serait un atout considérable si elle est confirmée dans un produit fini. Dans les centres de données IA, chaque watt économisé compte, que ce soit pour réduire la facture électrique, améliorer la gestion thermique, augmenter la densité par rack, ou renforcer la stabilité et la capacité de déploiement.

Une indication que la mémoire deviendra le nouveau terrain d’affrontement

HB3DM arrive à un moment où l’industrie redécouvre un principe que les architectes système anticipent depuis des années : le calcul ne sert pas à grand-chose si la mémoire ne peut alimenter le processeur à la vitesse requise. Avec l’essor de l’IA, cette limitation devient un enjeu commercial majeur.

Jusqu’à présent, la discussion portait surtout sur les GPU, accélérateurs et nodes de fabrication. Mais le goulot d’étranglement de la mémoire gagne du terrain. La HBM, coûteuse, complexe à produire, limitée en approvisionnement et exigeante en termes d’emballage, pourrait voir sa position évoluer si de nouvelles alternatives offrent davantage de bande passante, moins de consommation ou une meilleure scalabilité.

La question reste à savoir si ZAM pourra passer du stade de démonstration technique à une production viable, rentable, et conforme aux besoins des grands concepteurs d’accélérateurs. L’histoire du matériel regorge d’architectures prometteuses qui n’ont pas franchi la barrière industrielle. En mémoire, ce saut est encore plus difficile : il demande performance, fiabilité, capacité, coût, volume de production, et plusieurs années de validation client.

Intel et SoftBank proposent une idée intéressante, mais qui reste à tester encore. HB3DM ne remplacera pas immédiatement la HBM4 sur la base d’un simple débit. Il devra prouver sa capacité à évoluer, à augmenter sa capacité, à garantir une fabrication viable, et à convaincre les intégrateurs d’accélérateurs qu’il offre une valeur ajoutée réelle plutôt qu’une simple curiosité technique.

Ce qui est captivant, c’est que la compétition ne se limite plus à améliorer la HBM existante. La pression de l’IA pousse à explorer de nouvelles voies comme la mémoire 3D, l’emballage avancé, les chiplets, l’interconnexion, ou encore le contrôle du consommable. HB3DM pourrait devenir un de ces axes. Si cette technologie finit par fonctionner, cela redonnerait à Intel une voix significative dans la mémoire avancée. Sinon, cela confirmera simplement la direction prise par le secteur : la prochaine bataille de l’IA se jouera aussi dans les micromètres qui séparent une couche mémoire d’une autre.

Questions fréquentes

Qu’est-ce que HB3DM ?

HB3DM est une proposition de mémoire 3D basée sur Z-Angle Memory, développée dans le cadre d’une collaboration entre Intel et SAIMEMORY, filiale de SoftBank. Elle vise à offrir un haut débit et une faible consommation pour l’intelligence artificielle et le HPC.

En quoi différencie-t-elle de la HBM ?

HB3DM utilise également un empilement vertical mais mise sur une intégration 3D extrêmement fine, avec des couches de DRAM de 3 µm, un hybrid bonding et une couche logique en dessous pour piloter le transfert de données.

Est-elle déjà une alternative commerciale à la HBM4 ?

Pas encore. La technologie est au stade de démonstration technique. SoftBank prévoit des prototypes pour 2027 et une commercialisation en 2029.

Quelle est sa principale avantage et sa limite majeure ?

L’atout principal est le débit, estimé à environ 5,3 TB/s par empilement. La principale limite est la capacité initiale, autour de 9-10 GB, nettement inférieure à celle de la HBM4.

Nouveauté d’@Intel et @SoftBank SAIMEMORY lors de @VLSI_2026

Paper T17.5Première démo de HB3DM

➡️ 9 couches, 3 µm par empilement

➡️ 1 couche logique + 8 couches DRAM

➡️ 13,7k TSV par couche avec hybrid bonding

➡️ 1,125 GB par couche, donc 10 GB par empilement

➡️ Bande passante de 0,25 Tb/sec/mm²

➡️ Die de 171 mm², soit 10 … pic.twitter.com/q79qV4sRdT— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) 29 avril 2026