L’industrie des semi-conducteurs continue d’évoluer, mais chaque nouveau saut technologique demande plus de temps, davantage d’investissements et des changements d’architecture plus complexes. L’idée ancienne selon laquelle les transistors devenaient simplement plus petits génération après génération ne suffit plus à expliquer la situation actuelle. À l’ère de l’angstrom, l’amélioration proviendra d’une combinaison beaucoup plus sophistiquée : nouveaux types de transistors, empilement vertical, matériaux alternatifs, interconnexions plus fines, alimentation par la face arrière du wafer et packaging avancé.

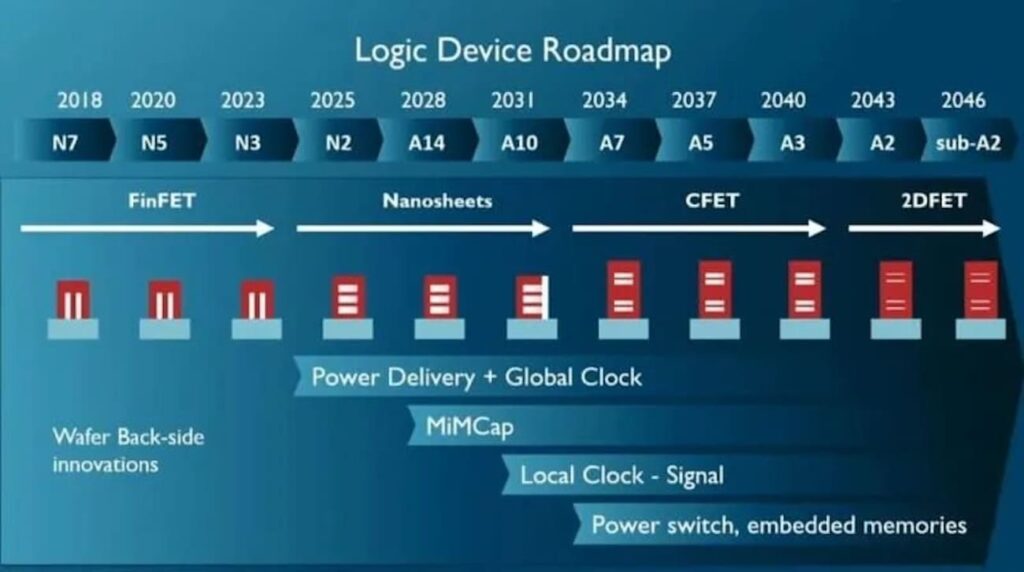

Le calendrier stratégique attribué à imec, le centre belge de recherche en nanoélectronique, situe le premier nœud en dessous de 1 nm vers 2034. Ce jalon correspondrait au nœud A7, équivalent à 0,7 nm ou 7 angstroms, marquant l’entrée dans la classification des CFET, une architecture où transistors nMOS et pMOS s’empilent verticalement pour continuer à augmenter la densité logique. Plus tard, autour de 2043, apparaîtraient les FET 2D au nœud A2, utilisant des matériaux bidimensionnels comme voie potentielle pour dépasser les limites actuelles de miniaturisation.

Il est important de préciser que ces chiffres ne doivent pas être compris comme des promesses de production commerciale immédiate. Dans l’univers des semi-conducteurs, la dénomination des nœuds ne décrit plus une dimension physique réelle du transistor, mais une étiquette technologique et commerciale. Le calendrier indique surtout des phases de recherche et développement, et non une certitude que tel ou tel fabricant commercialisera des chips de 0,7 nm dès 2034 ou de 0,2 nm en 2043. Néanmoins, ce plan aide à mieux comprendre l’orientation du secteur.

Moore n’est pas mort, mais il ne marche plus tout à fait droit

Pendant des décennies, l’industrie s’est appuyée sur une réduction très agressive de la taille des transistors. Entre la fin des années 1990 et le début des années 2000, la densité logique permettait de doubler prestations ou de réduire les coûts à chaque génération. Ce rythme s’est désormais ralenti. La réduction de l’aire des cellules SRAM, un indicateur clé de la scalabilité des nœuds, a perdu en vitesse ces dernières années; les nœuds récents montrent une progression beaucoup plus marginale.

Le problème ne se limite pas à la physique. La fabrication à l’échelle des nœuds avancés exige une lithographie EUV sophistiquée, des processus plus complexes, davantage de masques, plus d’étapes de fabrication, et d’énormes investissements dans les usines. C’est la raison pour laquelle les grands fabricants et concepteurs de puces se tournent de plus en plus vers les chiplets, la 2,5D, la 3D IC, les interposers et le packaging avancé. Plutôt que d’intégrer tout sur une seule dièce gigantesque, ils combinent des blocs spécialisés fabriqués sur différents nœuds et connectés via des techniques de plus en plus sophistiquées.

L’intelligence artificielle et le calcul haute performance ont accéléré cette tendance. Les accélérateurs modernes ne dépendent plus uniquement de transistors plus fins ; ils nécessitent également une mémoire HBM à proximité du processeur, des interconnexions à très haut débit, une alimentation efficace, et une gestion thermique optimale. La course ne se joue pas seulement sur le nœud, mais sur le système dans son ensemble.

Cependant, la logique de progression se poursuit. La feuille de route prévoit une transition claire du FinFET vers les nanosheets, puis vers les CFET, et ultérieurement vers des transistors à base de matériaux 2D. Chaque étape vise à résoudre le même défi : comment augmenter la densité et la performance lorsque la réduction horizontale classique atteint ses limites.

| Période approximative | Nœud | Architecture prévue | Idée principale |

|---|---|---|---|

| 2018-2023 | N7, N5, N3 | FinFET | Dernière évolution majeure du FinFET sur des nœuds avancés |

| 2025 | N2 | Nanosheet / GAA | Introduction des transistors à porte tout autour (Gate-All-Around) |

| 2028 | A14 | Nanosheet amélioré | Plus de densité et ajustements architecturaux |

| 2031 | A10 | Nanosheet avancé | Dernière étape avant le sous-1 nm |

| 2034 | A7 | CFET | Premier nœud en dessous de 1 nm prévu |

| 2037 | A5 | CFET amélioré | Plus de scalabilité verticale et optimisation |

| 2040 | A3 | CFET avancé | Extension de l’architecture CFET |

| 2043 | A2 | FET 2D | Introduction des matériaux bidimensionnels |

| 2046 | Sub-A2 | FET 2D avancé | Scénario de continuité au-delà de 0,2 nm |

CFET et FET 2D : la stratégie d’empilement et de changement de matériaux

La prochaine étape immédiate est la transition vers les nanosheets FET, aussi connus sous le nom de GAA ou gate-all-around. L’idée est d’enrouler le canal du transistor autour de la porte, renforçant ainsi le contrôle électrique par rapport au FinFET. TSMC, Samsung et Intel ont déjà préparé leurs variantes de cette transition, avec des noms commerciaux et des calendriers spécifiques.

La grande étape suivante serait le CFET, où les transistors nMOS et pMOS s’empilent verticalement au lieu d’être disposés en surface. Cette configuration permet de réduire la surface de la cellule et d’accroître la densité sans se limiter à une simple réduction des dimensions horizontales. Selon imec, le CFET est une architecture prometteuse pour des nœuds en dessous de 1 nm, avec diverses options d’intégration, notamment monolithique ou séquentielle.

Le saut ultérieur concernerait les FET 2D. Il ne s’agit plus seulement de réorganiser le silicium, mais d’introduire des matériaux bidimensionnels dans le canal. Ces matériaux conservent des propriétés électriques utiles à des échelles extrêmes. La difficulté réside dans leur intégration industrielle, en garantissant performance, uniformité, contacts électriques fiables et durabilité. La recherche est prometteuse, mais la fabrication en production de masse reste confrontée à de nombreux défis.

C’est pourquoi l’horizon 2043-2046 doit être abordé avec prudence. Il ne s’agit pas d’une date de sortie de produit, mais d’une vision de recherche indiquant les étapes possibles si l’industrie parvient à résoudre les enjeux liés aux matériaux, procédés, interconnexions, alimentation et dissipation thermique.

Le goulot d’étranglement des connexions

Réduire la taille d’un transistor n’est pas suffisant si le véritable obstacle réside dans les connexions entre eux. La partie BEOL, responsable des couches métalliques connectant les dispositifs, constitue une zone critique. À mesure que les espacements métalliques se réduisent, la résistance, la congestion et les problèmes thermiques augmentent. Le cuivre, jusque-là dominant, commence à montrer ses limites à ces échelles extrêmes en raison des barrières nécessaires et de la perte de volume utile.

La feuille de route prévoit une transition progressive vers des matériaux comme le rutenium, et des techniques telles que semi-damascène ou métallisation soustractive, ainsi que l’utilisation de gaps d’air et de vias auto-alignés. Vers 2025, on parle de espacements métalliques minimaux de 24 à 26 nm ; en 2028, ils descendront à 20-22 nm ; en 2031, entre 18 et 20 nm ; et en 2034, en dessous de 20 nm, avec une ambition pour 2037-2040 de réduire encore à 12-16 nm, voire moins, dans la recherche.

| Année approximative | Nœud | Pitch métallique minimal | Technologie BEOL privilégiée |

|---|---|---|---|

| 2025 | N2 | 24-26 nm | Cuivre, semi-damascène |

| 2028 | A14 | 20-22 nm | Améliorations des procédés existants |

| 2031 | A10 | 18-20 nm | Transition vers le rutenium, gaps d’air et vias auto-alignés |

| 2034 | A7 | 16-18 nm | Semi-damascène ou métallisation soustractive |

| 2037-2040 | A5/A3 | 12-16 nm | Matériaux alternatifs en cours d’étude |

Ce point est souvent peu abordé dans le débat public, qui met plutôt l’accent sur la dénomination des nœuds tels que “2 nm” ou “1,4 nm”. Pourtant, il reste crucial. Un chip ne s’améliore pas uniquement par la densité accrue de ses transistors. Si l’alimentation, les signaux ou la dissipation thermique ne suivent pas, le rendement réel sera limité ou la consommation s’envolera.

Alimentation backside et gestion thermique

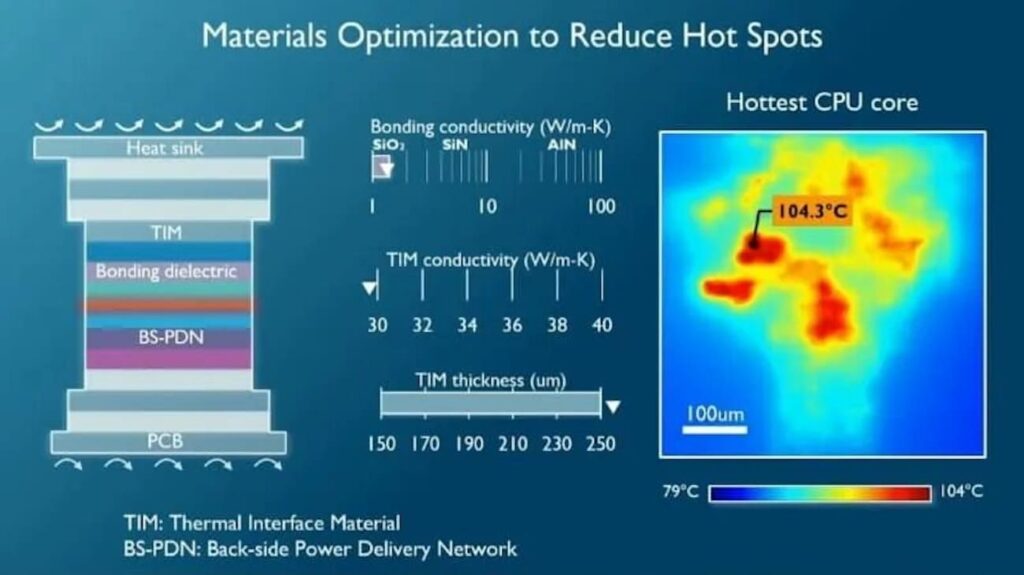

Une autre pièce essentielle concerne l’alimentation électrique. Traditionnellement, celle-ci transite par la face avant du wafer, partageant l’espace avec les couches métalliques de signalisation. La distribution d’alimentation par la face arrière, ou backside power delivery network (BSPDN), consiste à dévier une partie de cette alimentation pour libérer la face avant pour les signaux. Son avantage est évident : réduire la congestion, améliorer la fourniture de courant, augmenter les marges de scalabilité.

Mais ce n’est pas sans compromis. Modifier le routage de l’alimentation impacte aussi la dissipation thermique, car les chemins thermiques sont modifiés. L’analyse technique d’imec souligne la nécessité d’étudier attentivement ces options, en tenant compte des contraintes thermiques. Sur les puces de haute performance, où la gestion de la chaleur est critique, chaque modification de la structure physique doit être soigneusement optimisée.

La feuille de route évoque également l’intégration de régulateurs de tension dans la carte, le boîtier, l’interposer ou directement dans le wafer. Pour l’IA et le HPC, alimenter des ensembles complexes comprenant chiplets, HBM et accélérateurs requiert une architecture électrique très précise. La puissance ne peut plus être considérée comme un simple paramètre externe, elle devient partie intégrante du design systémique avancé.

C’est là le véritable message de cette vision stratégique : le futur des semi-conducteurs ne repose pas uniquement sur une technologie unique mais sur la coordination d’innovations en transistors, câblage, alimentation, matériaux, packaging 3D, mémoire locale et gestion thermique. La miniaturisation poursuit sa route, mais elle ne relève plus d’une seule avancée isolée.

La réalisation des chips sous-1 nm, si elle se concrétise comme prévu, ne sera pas une simple transition de nœud. Ce sera le fruit d’un effort technique quasi-décennal, allant des nanosheets actuels aux CFET, puis aux matériaux 2D. Parallèlement, l’industrie devra justifier économiquement chaque étape. Avec des usines de plus en plus coûteuses et un packaging avancé qui prend en main une part croissante du système, tous les produits ne nécessiteront pas le nœud le plus avancé.

Les grands acteurs de l’IA, les CPU haute performance et les puces pour centres de données continueront à repousser les limites. Le reste du marché mélangera probablement nœuds mûrs, chiplets et packaging pour équilibrer coûts et performances. Moore est bel et bien toujours là, mais il est devenu plus coûteux, plus vertical, et beaucoup plus complexe à représenter par une simple chiffre en nanomètres.

Questions fréquentes

Quand les puces sous 1 nm seront-elles disponibles ?

Le calendrier d’imec prévoit un premier nœud sous 1 nm vers 2034, avec le A7 (0,7 nm) basé sur la technologie CFET. Cependant, cette date ne garantit pas une production commerciale immédiate.

Qu’est-ce qu’un CFET ?

Un CFET (Complementary FET) consiste en l’empilement vertical de dispositifs nMOS et pMOS, permettant d’accroître la densité logique au-delà des nanosheets classiques.

Que sont les FET 2D ?

Ce sont des transistors utilisant des matériaux bidimensionnels dans leur canal, étudiés comme une solution pour poursuivre la scalabilité jusqu’à des nœuds de 0,2 nm et moins.

Pourquoi ne suffit-il plus de simplement réduire la taille du transistor ?

Parce que les limites actuelles concernent aussi les interconnexions, l’alimentation, la gestion thermique, la mémoire et par-dessus tout le coût de fabrication. La performance moderne dépend de l’intégration systémique globale.

source : 36kr