SK hynix a franchi une étape technique importante dans l’évolution de la mémoire HBM en vérifiant une pile de 12 couches assemblée par hybride bonding, une technologie d’emballage avancée qui pourrait jouer un rôle clé dans les prochaines générations de mémoire à haute bande passante. La société sud-coréenne n’a pas communiqué de chiffres précis sur les performances de fabrication, mais elle a reconnu travailler à augmenter le taux de rendement (yield) pour atteindre un niveau viable pour la production en masse.

Annonce faite par Kim Jong-hoon, responsable technique de SK hynix, lors de la conférence Beyond HBM tenue à Séoul, cette avancée intervient dans un contexte de compétition accrue avec les générations HBM4 et HBM5. La demande croissante de puces pour l’intelligence artificielle a fait de cette mémoire l’un des composants les plus rares et stratégiques du marché. NVIDIA, AMD, Google, Amazon et d’autres concepteurs de puces nécessitent toujours plus de capacité, de bande passante et une consommation électrique réduite pour alimenter GPU, TPU et architectures d’IA à grande échelle.

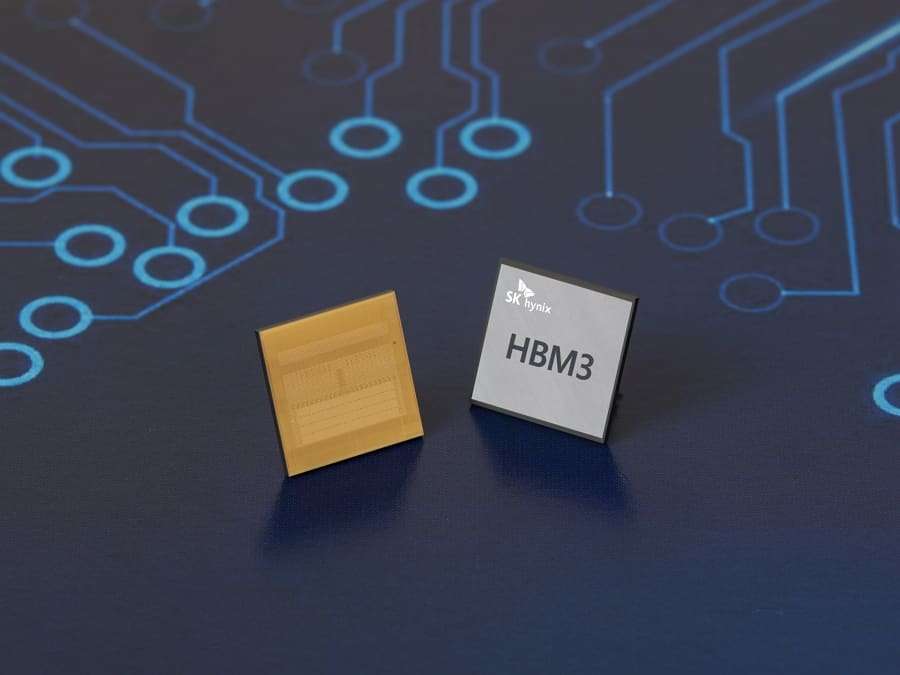

Ce que l’hybride bonding apporte à la mémoire HBM

La mémoire HBM est construite en empilant plusieurs puces DRAM verticalement et en les connectant via des TSVs (Through-Silicon Vias) et des interconnexions internes. Jusqu’à présent, les techniques les plus répandues utilisaient des bumps ou microbumps pour assembler les couches, une méthode mature mais avec des limites physiques : encombrement, résistance accrue, génération de chaleur, et complexité à augmenter le nombre de couches sans alourdir le boîtier.

Le hybrid bonding cherche à réduire ces limitations en connectant directement les surfaces des puces, généralement par contacts cuivre-cuivre et diélectrique-diélectrique. En éliminant ou en diminuant la dépendance aux bumps, cette technologie permet des interconnexions plus denses, une pile plus compacte, une meilleure efficacité électrique et, en théorie, une production thermique moindre. Pour la mémoire HBM, où chaque millimètre et chaque watt comptent, ces améliorations peuvent faire la différence.

SK hynix a indiqué avoir déjà vérifié une structure HBM de 12 couches en hybrid bonding. La société n’a pas fourni de chiffres sur le taux de rendement, ce qui est une omission importante car le défi principal de cette technologie ne réside pas seulement dans la démonstration de la principe, mais dans sa fabrication à une échelle suffisamment performante, rentable et reproductible. Kim Jong-hoon a souligné que les préparations sont « nettement plus avancées qu’auparavant », tout en évitant de donner des pourcentages précis.

Ce pragmatisme est compréhensible. Dans l’univers des semi-conducteurs, un processus peut être techniquement faisable sans être rentable si trop d’unités présentent des défauts. En HBM, le problème est amplifié car une pile intègre de nombreuses couches : si l’une d’entre elles échoue, tout le module peut perdre de la valeur ou devenir inutilisable. C’est pourquoi le taux de rendement du processus d’emballage est si critique.

MR-MUF restera en place jusqu’à la nouvelle étape

SK hynix ne prévoit pas d’abandonner immédiatement sa technologie actuelle. La société poursuivra l’utilisation du MR-MUF (Mass Reflow Molded Underfill) jusqu’à ce que le hybrid bonding soit mature. Le MR-MUF utilise des bumps en cuivre et remplit l’espace entre les couches avec du matériau underfill après chauffage, étant une technologie clé qui a permis à SK hynix de progresser avec la HBM3E et la HBM4.

La transition sera progressive. La HBM4 est déjà en production avec des techniques avancées d’emballage, mais le hybrid bonding semble plus associé à des générations ultérieures ou à des configurations plus denses. Certaines prévisions de marché estiment qu’une adoption plus large du hybrid bonding pourrait intervenir avec HBM5, vers 2029 ou 2030, lorsque le besoin d’empiler davantage de couches et de mieux gérer la thermique sera encore plus crucial.

Le contexte technique éclaire cette tendance. La HBM4 marque déjà une avancée par rapport à la HBM3E : elle double l’interface à 2 048 bits, augmente le nombre de canaux, et accroît le débit par pile. La spécification HBM4, selon JEDEC, prévoit une capacité accrue et des configurations pouvant atteindre 16 couches, avec une orientation claire vers l’IA et le HPC. Pour atteindre 16, 20 ou plus de couches dans de futures architectures, les méthodes traditionnelles sont de plus en plus limitées.

C’est ici que le hybrid bonding devient une option attrayante. Plus on empile de couches, plus il est difficile de contrôler la hauteur, la gestion thermique, l’alignement et la fiabilité mécanique. Réduire la distance entre dies et améliorer la connectivité électrique peut permettre des modules plus denses et plus performants, même si le processus de fabrication devient plus exigeant.

L’enjeu majeur de la HBM réside dans l’emballage

Depuis des années, la mémoire s’expliquait principalement par ses processus de fabrication, capacités et vitesses. À l’ère de l’IA, l’emballage avancé devient un élément central. La HBM n’est pas simplement une DRAM rapide : c’est une architecture 3D complexe qui doit cohabiter avec GPU, interposers, substrats avancés, logique de support, refroidissement et alimentation électrique.

SK hynix, Samsung et Micron rivalisent pour sécuriser leurs clients pour la HBM4 et préparer les générations HBM4E et HBM5. SK hynix a une longueur d’avance grâce à sa position en tant que fournisseur clé pour NVIDIA, mais ses concurrents accélèrent. Micron, par exemple, a annoncé des avancées pour la HBM4 destinée à de nouvelles plateformes, tandis que Samsung tente de regagner du terrain après plusieurs cycles où SK hynix a dominé la demande liée à l’IA.

La compétition ne porte pas uniquement sur la capacité à vendre plus de mémoire, mais aussi sur la capacité à répondre à des exigences de plus en plus exigeantes des grands designers d’accélérateurs. NVIDIA a relevé les standards en termes de vitesse, consommation, capacité, intégration et calendrier. La HBM4 intégrant une logique personnalisée complique aussi le changement de fournisseur sans nouveaux redémarrages ou validations, ce qui confère une valeur stratégique à celui qui arrive en premier, tout en augmentant le coût d’erreur.

Les investissements suivent cette tension. SK hynix a récemment annoncé une dépense d’environ 19 trillions de wons, soit près de 12,85 milliards de dollars, pour une nouvelle usine en Corée du Sud, afin de répondre à la demande en mémoire IA, avec un focus sur l’emballage avancé. La société a également indiqué que la demande de HBM pour les années à venir dépasse son offre, ce qui suggère que la pénurie risque de persister.

Impacts pour les centres de données IA

La mémoire HBM constitue l’un des principaux goulets d’étranglement dans l’intelligence artificielle moderne. Les grands modèles nécessitent non seulement une puissance de calcul considérable, mais aussi une alimentation rapide en données pour alimenter les accélérateurs. Si la mémoire ne fournit pas un bande passante suffisante, la GPU ou l’accélérateur peut rester en attente, même si la puissance brute est disponible.

Les progrès dans la mémoire HBM influent directement sur le coût et les performances des centres de données IA. Plus de couches signifient une capacité accrue par module. Un débit plus élevé permet une meilleure utilisation de l’accélérateur. Une meilleure efficacité thermique peut réduire la consommation électrique et permettre des systèmes plus denses. Toutefois, si l’emballage n’évolue pas avec un bon yield, cela pourrait se traduire par une mémoire plus coûteuse et moins accessible.

Le hybrid bonding offre une solution partielle à ces enjeux, mais cette technologie n’est pas encore prête pour un déploiement massif et présente ses propres défis. La précision d’alignement, la propreté des surfaces, le contrôle des défauts, les processus thermiques et la métrologie doivent être maîtrisés avec une extrême finesse. Dans une pile HBM, ne serait-ce qu’un petit défaut peut compromettre l’ensemble. C’est pourquoi SK hynix évoque une avancée, non une mise en œuvre généralisée immédiate.

Ce constat envoie un message clair au marché : l’avenir de l’IA ne dépendra pas uniquement des nouvelles GPU, mais également de la façon dont seront fabriquées, connectées et refroidies les mémoires qui les alimentent. La performance d’une plateforme IA sera de plus en plus liée à l’emballage avancé. Et là, SK hynix souhaite conserver sa position, face à la concurrence de Samsung et Micron qui ne tarderont pas à réduire l’écart.

Questions fréquentes

Que vient de vérifier SK hynix ?

SK hynix a validé une pile de 12 couches HBM assemblée en hybrid bonding, une technique d’union directe entre dies visant à améliorer densité, performance et efficacité.

Qu’est-ce que l’hybrid bonding en mémoire HBM ?

C’est une méthode d’emballage qui connecte directement les surfaces de puces, en réduisant ou éliminant l’usage de bumps. Elle peut augmenter le débit, réduire la consommation, diminuer la hauteur de la pile et maîtriser la thermique.

SK hynix produit-elle déjà à grande échelle des HBM utilisant cette technologie ?

Pas encore. La société indique qu’elle travaille pour améliorer le taux de rendement, mais aucune production commerciale n’a été confirmée à ce stade.

Pourquoi cette avancée est importante pour l’IA ?

Parce que les accélérateurs IA ont besoin de mémoire HBM à large bande passante et haute capacité. Améliorer l’emballage peut permettre des modules plus denses, plus rapides et plus efficaces pour les futures GPU et systèmes HPC.

source : wccftech