SK hynix a dévoilé sa feuille de route la plus ambitieuse à ce jour lors du SK AI Summit 2025. Ce n’est pas simplement un calendrier avec plus de couches et plus de MHz : c’est une vision axée sur l’IA qui couvre la mémoire à large bande passante (HBM), la DRAM conventionnelle, le NAND/SSD et de nouveaux blocs “intelligents” promettant de faire passer le calcul au-delà de la barrière de la mémoire. La société distingue deux étapes avec des objectifs très clairs :

- 2026–2028 : déploiement agressif de HBM4/HBM4E et arrivée du LPDDR6 ; optimisation de la DRAM pour réduire le coût total en datacenter ; transition vers le PCIe 6.0 pour les SSD.

- 2029–2031 : consolidation et nouvelle vague avec HBM5/HBM5E (standard et sur mesure), DDR6, GDDR7-Next (la base de la future GDDR8), 3D DRAM, PCIe 7.0 pour les SSD, UFS 6.0 pour mobiles, et NAND 4D comptant plus de 400 couches.

Deux concepts clés émergent en chemin, traversant toutes les familles de produits :

- AI-D (IA-DRAM) : optimisation, rupture de la barrière de la mémoire et expansion vers de nouveaux segments avec CXL, PIM (traitement en mémoire) et formats comme MRDIMM ou SOCAMM2.

- AI-N (AI-NAND/Storage Next) : SSD et mémoires conscients de la charge IA, privilégiant performance, bande passante ou densité, selon le cas.

Voici un aperçu des pièces du puzzle et de leur importance.

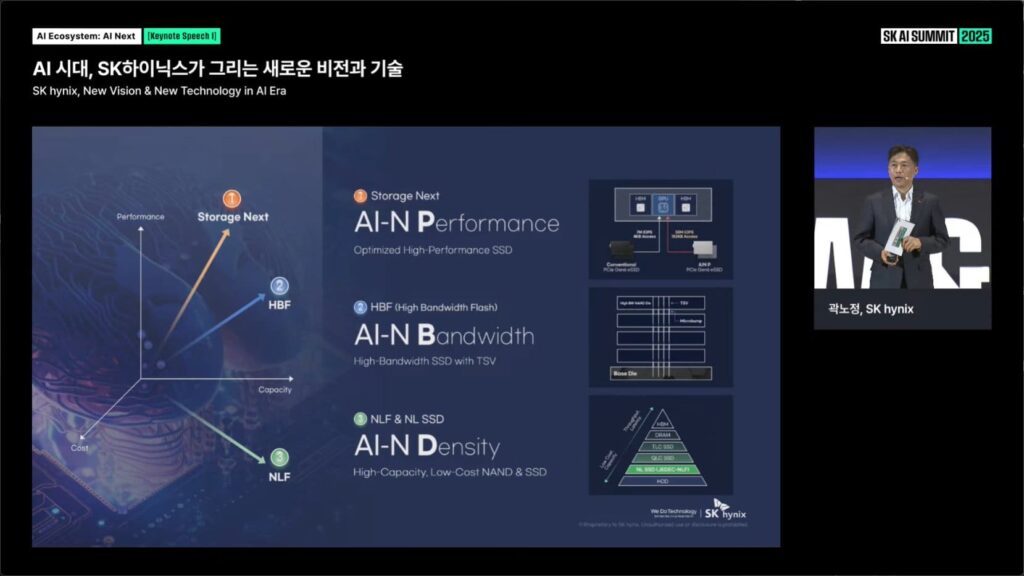

AI-N : trois “profils” de stockage pour l’ère IA

Dans l’ouverture de la présentation (“New Vision & New Technology in AI Era”), SK hynix a regroupé le stockage de demain en trois profils, tous sous l’égide AI-N :

- AI-N Performance (Storage Next) : SSD optimisés pour haut rendement. La société a montré un schéma avec des chemins d’accès PCIe Gen6 eSSD et une hiérarchie où le SSD s’intègre dans un tissu à faible latence aux côtés de CPU, GPU, HBM et NIC. L’idée : minimiser les goulots d’étranglement E/S dans des charges de travail token-intensives et de fenêtres de contexte croissantes.

- AI-N Bandwidth (HBF – High Bandwidth Flash) : un SSD à large bande passante avec TSV. Le schéma technique reflète TSV et microbumps sur une die de base, réunissant des matrices de flash avec des interconnexions verticales pour augmenter le débit par rapport à un eSSD conventionnel. Le but : rapprocher — avec des coûts de NAND — les rythmes exigés pour l’entraînement et l’inférence massifs.

- AI-N Density (NLF & NL SSD) : NAND à très haute capacité et SSD à faible coût pour stockage massif. Sur la pyramide des niveaux (HDD → NL SSD → QLC/TLC SSD → DRAM → HBM), cette catégorie pousse la capacité vers le haut avec un coût par bit réduit, pour alimenter des lacs de données et des réservoirs de datasets en croissance continue.

Traduction pratique : la société ne voit pas un seul “SSD IA”, mais des familles spécialisées —performance, bande passante ou densité — qui se combineront dans les centres de données originaux IA.

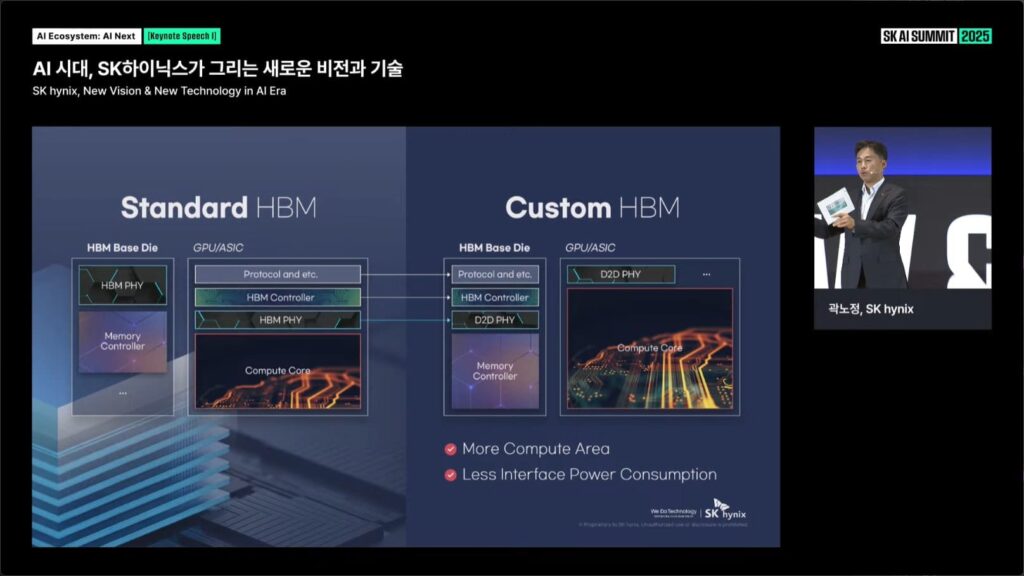

HBM standard vs HBM “sur mesure” : repositionner les pièces pour économiser des watts et gagner de la surface de calcul

Un autre point clé de la présentation oppose la HBM standard à la HBM personnalisée. Dans le design traditionnel, une grande partie des bloques d’interface (PHY/Contrôleurs) sont répartis entre la die HBM de base et le SoC/GPU. La proposition “Custom HBM” relocalise ces fonctions :

- Sur la die HBM de base sont intégrés le contrôleur HBM et un D2D PHY (die-à-die).

- Dans le SoC/GPU, la communication vers la HBM se limite à un D2D PHY plus léger.

Le résultat, selon SK hynix : plus d’espace dispo pour les noyaux de calcul sur la puce hôte, et une consommation réduite au niveau des interfaces. C’est une indication de l’orientation du marché : mémoire et calcul continueront à s’intégrer en conception conjointe (DTCO→STCO), notamment dans les accélérateurs IA.

AI-D : optimisation aujourd’hui, rupture de la barrière de la mémoire demain

Sous la marque AI-D (IA-DRAM), SK hynix structure sa stratégie DRAM autour de trois axes :

- Optimization (Lower TCO in Datacenter)

- MRDIMM, SOCAMM2 et LPDDR5R pour réduire coût total et consommation dans les racks de calcul. MRDIMM vise à augmenter la bande passante par module et SOCAMM2 à densité dans des facteurs compacts.

- Breakthrough (Au-delà de la barrière de la mémoire)

- CXL-CMM (mémoire poolable et cohérente via Compute Express Link), LPDDR6-PIM (traitement en mémoire) et GDDR AiM (accélération in-memory). L’objectif est de déplacer le calcul (réduire, rechercher, scatter/gather) au plus près des données, soulageant la pression sur les bus et les contrôleurs.

- Expansion (Dédicated à tous les usages)

- DRAM pour l’industrie / automobile (LPDDR/HBM) et LPDDR5X/LPDDR6 dans les appareils et edge, pour que l’IA sorte du centre de données sans sacrifier la fiabilité.

Implication pratique : cette stratégie ne se limite pas à une innovation en mémoire, mais vise à une approche intégrée du système mémoire, en favorisant la co-conception avec CPU, GPU et accélérateurs IA, pour maximiser l’efficacité et réduire la consommation.

Calendrier : 2026–2028 (déploiement) et 2029–2031 (nouvelle vague)

La dernière diapositive résume la feuille de route en quatre lignes verticales (HBM, DRAM conventionnelle, AI-D DRAM, NAND). Voici les étapes clés :

2026–2028

- HBM (standard) : HBM4 16-Hi ; HBM4E en 8/12/16-Hi.

- HBM (sur mesure) : Custom HBM4E pour clients IA/supercalcul.

- DRAM conventionnelle (standard) : LPDDR6 comme nouvelle norme pour mobiles et portables.

- AI-D : LPDDR5X en SOCAMM2, MRDIMM Gen2, LPDDR5R; 2e génération CXL et premières LPDDR6-PIM.

- NAND (standard) : PCIe Gen5 eSSD (avec capacités cibles dépassant 200 TB en QLC dans certains roadmaps), passages à PCIe Gen6 eSSD/cSSD et UFS 5.0 pour mobiles.

- NAND (AI-N) : lancement de AI-N D (famille axée sur densité et gestion prédictive des données).

Signification : un déploiement massif du HBM4/4E pour l’entraînement et l’inférence de modèles de dernière génération, des mobiles avec LPDDR6, et du SSD PCIe 6.0 en tant que nouvelle base pour les racks. La convergence CXL débute, et les premiers PIM commerciaux apparaissent.

2029–2031

- HBM (standard) : HBM5 et HBM5E.

- HBM (sur mesure) : variantes à mesure de HBM5/HBM5E.

- DRAM conventionnelle (standard) : GDDR7-Next (base de la prochaine GDDR8), DDR6 et 3D DRAM.

- AI-D : LPDDR6 sur SOCAMM2 (expansion), 3e génération CXL et PIM-Next (future de l’informatique en mémoire).

- NAND (standard) : PCIe Gen7 eSSD/cSSD, UFS 6.0 et NAND 4D de 400+ couches.

- NAND (AI-N) : AI-N P (Storage Next) et AI-N B (HBF) se perfectionnent, portant bande passante et optimisation IA en première ligne.

Signification : une nouvelle vague qui mariant HBM5 avec des accélérateurs de prochaine génération et amenant le DDR6/GDDR7-Next au PC et au gaming. En stockage, PCIe 7.0 dans les data centers, UFS 6.0 sur mobiles, et du NAND 4D dépassant les 400 couches.

Implications : IA, gaming, mobiles et edge

- Entraînement et inférence de pointe : HBM4E→HBM5 et HBF (flash avec TSV) élargiront le pipeline de données depuis le SSD jusqu’au GPU/ASIC, réduisant les goulots d’étranglement dans les pipelines token-intensifs et de longs contextes.

- PC et gaming : GDDR7-Next et DDR6 augmenteront bande passante et latence ; la mention de 3D DRAM indique une potentialité de empilements verticaux pour des densités accrues.

- Mobiles et edge : LPDDR6 comme base, UFS 6.0 au second semestre 2020, et LPDDR6-PIM pour inférence locale avec efficacité énergétique. Applications dans automobile et industrie avec des mémoires de niveau industriel.

- Architectures memory-centric : CXL (Gen2→Gen3) habilite des pools de mémoire partagée et une extension déconnectée; PIM et AiM (in-memory accéléré) rapprochent les opérations du donnée, clé pour réduire les latences p99.

- Durabilité : bien que aucune donnée PUE/WUE n’ait été fournie dans les diapositives, le déplacement vers HBM5/HBM5E et HBM personnalisée vise à réduire la consommation via la diminution de la puissance dans les interfaces et à augmenter la surface de calcul par die, deux facteurs critiques pour la consommation dans les racks IA.

Ce qui distingue cette feuille de route

- Memorisation comme système, et non comme composant : custom HBM, CXL, PIM et AiM indiquent une co-conception avec CPU/GPU/ASIC.

- Stockage “conscient” IA : AI-N différencie les profils (Performance/Bande passante/Densité) et anticipe le flash à haute bande passante (HBF) avec TSV.

- Calendrier étendu et cohérent : la vision s’étend jusqu’en 2031, reliant familles (HBM, DRAM, NAND) avec des points de croisement clairs entre les étapes.

Si SK hynix parvient à respecter cette feuille de route, elle ne se contente pas simplement d’accompagner l’IA : elle pourrait fixer le rythme et influencer la conception des accélérateurs, serveurs et dispositifs finaux pour la prochaine décennie.

Ce qu’il faut surveiller à partir de 2026

- HBM4E 16-Hi dans les accélérateurs commerciaux et adoption croissante du custom HBM (économie d’énergie et espace réel).

- Latences et débit de HBF par rapport aux eSSD PCIe 6.0 traditionnels.

- Commercialisation de la deuxième génération de CXL (latence accrue, pile logicielle et orchestration).

- Premiers démos de LPDDR6-PIM et GDDR AiM dans des cas réels (filtrage, reduce, recherches).

- Évolution de la densité en NAND 4D vers les plus de 400 couches annoncées pour 2029–2031.

Questions fréquentes (FAQ)

Quand la HBM5 sera-t-elle commercialisée selon SK hynix ?

Elle devrait faire son apparition dans la deuxième étape du roadmap, entre 2029 et 2031. SK hynix envisage de lancer HBM5 et HBM5E en versions standard et personnalisée, destinées aux accélérateurs IA et aux GPU de prochaine génération.

Qu’est-ce que la HBF (High Bandwidth Flash) et comment se différencie d’un SSD classique ?

La HBF est une notion de flash à large bande passante utilisant des TSV et microbumps pour augmenter le débit effectif par rapport à un eSSD PCIe traditionnel. Elle ne remplace pas la HBM ; elle rapproche le stockage des rythmes requis pour l’entraînement et l’inférence à grande échelle.

Quelles technologies de DRAM verrons-nous entre 2026 et 2028, et après 2029 ?

Entre 2026 et 2028 : LPDDR6 comme norme, MRDIMM Gen2, SOCAMM2, CXL Gen2 et premières LPDDR6-PIM. Après 2029 : DDR6, GDDR7-Next (base de GDDR8), 3D DRAM, CXL Gen3 et PIM-Next.

En quoi SK hynix innove-t-elle pour le stockage mobile et de datacenter au-delà de 2028 ?

Pour le datacenter : PCIe Gen7 eSSD et NAND 4D de 400+ couches vers 2029–2031. Pour mobile : UFS 6.0 et la continuité de LPDDR6 comme norme mémoire, avec PIM et variantes AI-N axées sur la densité et l’efficacité.

Sources

- SK AI Summit 2025 – Présentation “AI Ecosystem: AI Next | SK hynix, New Vision & New Technology in AI Era” (diapositives de keynote avec graphiques AI-N, AI-D, comparatif HBM standard vs HBM sur mesure et feuille de route 2026–2031).

- Matériel visuel officiel de SK hynix présenté durant la conférence (captures d’écran fournies).

RCS Universal Profile 4.0 est désormais officiel : comment se compare au SMS, aux versions précédentes de RCS et à WhatsApp