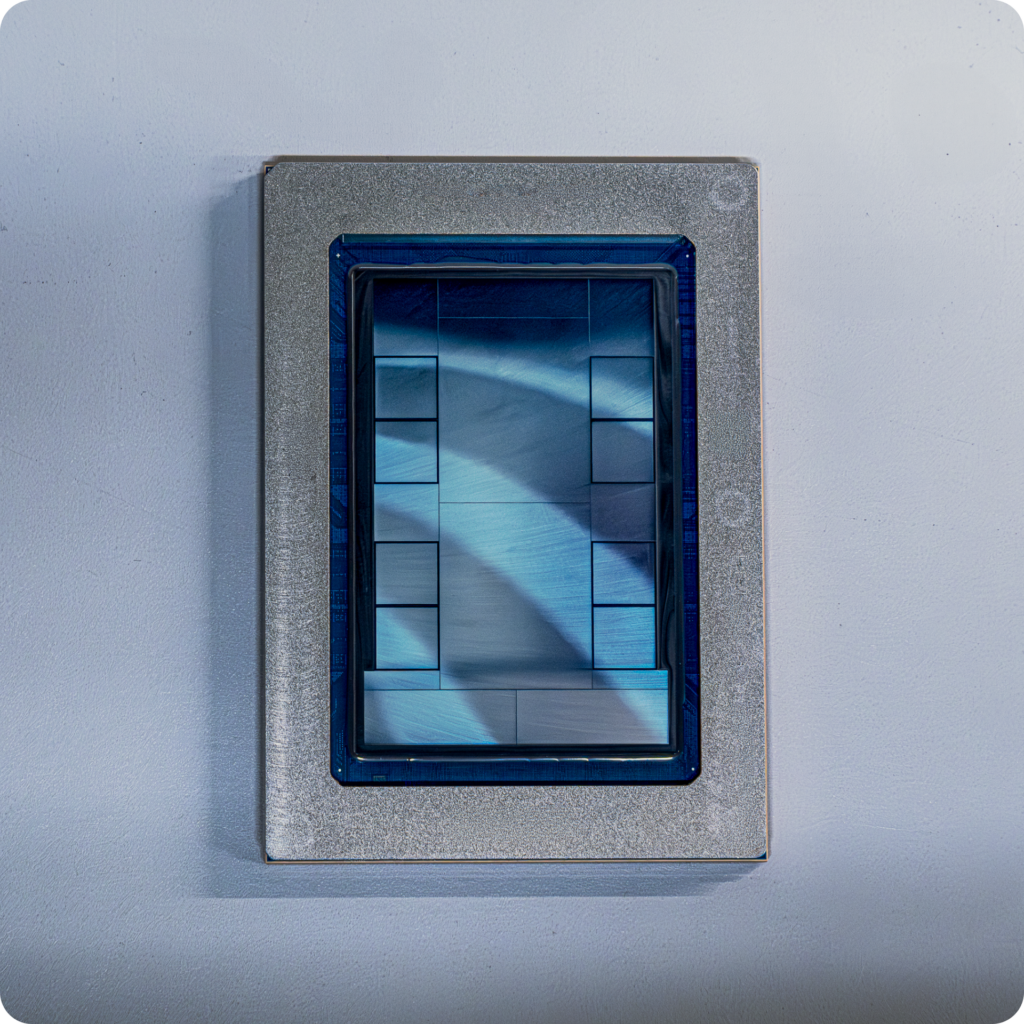

Meta a décidé d’accélérer le déploiement de sa famille d’accélérateurs propriétaires MTIA, renforçant ainsi une tendance clairement perceptible parmi les géants de l’hyperéchelle : réduire leur dépendance à une seule architecture GPU pour l’inférence en IA. Dans un article technique publié par la société, Meta détaille quatre nouvelles générations de sa ligne Meta Training and Inference Accelerator — MTIA 300, 400, 450 et 500 — dont certains déploiements ont déjà commencé ou sont prévus entre 2026 et 2027. Le message central est clair : l’inférence en IA nécessite des puces optimisées différemment de celles principalement conçues pour l’entraînement.

C’est une évolution qui s’inscrit dans une dynamique plus large du secteur. Google a déjà lancé Ironwood, sa première TPU conçue spécialement pour l’“ère de l’inférence”, tandis qu’AWS développe ses familles Trainium et Inferentia. Microsoft, quant à elle, a présenté Maia 200 comme son nouvel accélérateur interne dédié aux charges d’inférence. Si cette transition ne signifie pas encore un remplacement total de Nvidia, elle traduit toutefois une diversification croissante au niveau du silicium, où le coût par token et l’efficacité énergétique deviennent aussi importants que la puissance brute.

Meta explique que sa famille MTIA, développée “en étroite collaboration avec Broadcom”, continuera à jouer un rôle clé dans sa stratégie d’infrastructure IA, aux côtés d’autres solutions internes et externes. La société affirme avoir déjà déployé des centaines de milliers de puces MTIA en production et testé ces accélérateurs avec ses modèles internes ainsi qu’avec des grands modèles de langage (LLMs) comme Llama. Cette base lui permet maintenant de suivre une feuille de route plus ambitieuse, avec un rythme d’itération bien plus rapide que la norme dans l’industrie.

Ce qui est le plus marquant dans cette annonce, ce n’est pas seulement le nombre de générations, mais aussi leur focus stratégique. Meta indique que, de MTIA 300 à MTIA 500, la bande passante HBM aura été multipliée par 4,5, tandis que la puissance de calcul aura été augmentée par un facteur 25, et ce, en moins de deux ans. Selon leur plan, MTIA 300 est déjà en production pour l’entraînement de modèles de classement et de recommandation ; MTIA 400 a passé ses tests en laboratoire et se prépare au déploiement en centres de données ; MTIA 450 sera déployé à grande échelle début 2027, et MTIA 500 arrivera dans la même année.

L’inférence comme nouvelle arène stratégique

Le raisonnement technique de Meta repose sur une idée précise : en inférence générative, le goulet d’étranglement ne se situe plus toujours au même endroit du système qu’en entraînement. La société insiste sur le fait que la bande passante de la mémoire HBM est l’un des facteurs clés pour la performance lors de l’inférence, notamment lors du décodage. C’est pourquoi elle affirme que MTIA 450 double la bande passante HBM par rapport à MTIA 400, et que MTIA 500 la porte encore à la hausse de 50 %, tout en augmentant capacité et performance grâce à des formats de faible précision adaptés à l’inférence.

Cette évolution stratégique est significative. Pendant des années, les GPU ont été l’étalon presque universel pour l’entraînement et le service des modèles. Mais les hypergiants commencent à comprendre que toujours utiliser le même type de matériel pour tous les usages n’est pas forcément l’approche la plus efficace, surtout lorsque l’inférence devient la majorité de la consommation totale de ressources informatiques. C’est ici que Meta, Google, AWS et Microsoft semblent converger : développer leurs propres puces pour des charges de travail prédictibles et volumineuses, tout en conservant la dominance des GPU pour l’entraînement de pointe et d’autres usages plus polyvalents.

Google l’a exprimé clairement avec Ironwood, qu’il décrit comme sa septième génération de TPU, conçue spécifiquement pour l’inférence, avec 192 Go de HBM3E, une bande passante de 7,37 TB/s et une scalabilité jusqu’à 9 216 accélérateurs. De son côté, AWS présente Trainium3 avec 144 Go de HBM3E et une bande passante de 4,9 TB/s par puce, ainsi que ses systèmes UltraServer pouvant accueillir jusqu’à 144 puces. Microsoft, en janvier 2026, a dévoilé Maia 200, un accélérateur dédié à l’inférence, fabriqué en processus 3 nm, doté de 216 Go de HBM3E, avec une bande passante de 7 TB/s et une amélioration de 30 % en performance par dollar par rapport à ses systèmes précédents.

Moindre dépendance à Nvidia, mais sans rupture radicale

Cela ne signifie pas que Nvidia perdra sa position centrale du jour au lendemain. En fait, Meta n’envisage pas du tout une telle rupture. La société insiste sur le fait qu’elle continuera d’utiliser un portfolio diversifié de silicium interne et externe. Le marché reconnaît toujours que l’entraînement des modèles de pointe et une grande partie de l’infrastructure à grande échelle restent largement dépendants des plateformes GPU de Nvidia. La différence réside dans la dynamique interne au sein de chaque hyperéchelle : si l’entraînement reste majoritairement sous contrôle GPU, l’inférence commence à migrer vers des accélérateurs spécialisés où les coûts opérationnels peuvent être mieux optimisés.

Un autre point à souligner chez Meta : la rapidité. La société indique avoir développé une capacité à lancer une nouvelle génération de puces environ tous les six mois, grâce à une architecture modulaire de chiplets et à la réutilisation du même châssis, rack et infrastructure réseau pour plusieurs générations. Cette compatibilité physique permettrait d’insérer de nouveaux composants sans redémarrer tout l’environnement de déploiement, une étape cruciale si l’on souhaite réellement réduire le cycle de développement, habituellement d’un à deux ans dans l’industrie.

Enfin, Meta mise fortement sur le logiciel open source et la portabilité sans friction. La société cite PyTorch, vLLM, Triton et l’écosystème OCP comme éléments fondamentaux de MTIA. Cela est stratégique : la bataille du silicium ne se limite pas au seul enjeu du chip, mais dépend aussi de la facilité à porter modèles, kernels et pipelines d’inférence entre différentes plateformes. Plus le stack sera interopérable, plus la possibilité pour les hypergéants de débrider une partie de leur volume de travail du système CUDA deviendra crédible.

Broadcom monte en puissance dans l’arrière-plan

Dans cette course, un acteur émerge peu à peu en second plan mais avec une influence décisive : Broadcom. Meta mentionne la société comme partenaire étroit dans le développement de MTIA, et OpenAI a annoncé en octobre 2025 une collaboration avec Broadcom pour déployer 10 GW d’accélérateurs IA sur-mesure. Même si chaque programme comporte ses particularités, ces alliances illustrent à quel point le design de silicium personnalisé est devenu une priorité stratégique, accessible uniquement à des entreprises disposant d’un capital et d’un déploiement à très grande échelle.

En somme, la conclusion n’est pas que Nvidia ait perdu le contrôle du marché, mais que l’industrie travaille déjà activement pour réduire sa dépendance à cette société dans tous les cas d’usage. Avec cette nouvelle famille MTIA, Meta s’inscrit dans une logique que partagent déjà d’autres géants : entraîner lorsque cela a du sens avec des GPU, mais servir une inférence massive avec du silicium dédié lorsque l’économie du système le justifie. Si l’inférence devient le principal moteur de la consommation d’IA dans les années à venir, cette stratégie pourrait peser bien plus qu’on ne le croit aujourd’hui.

Questions fréquentes

Qu’a exactement annoncé Meta avec MTIA ?

Meta a présenté quatre générations d’accélérateurs propriétaires — MTIA 300, 400, 450 et 500 — avec des déploiements en production ou prévus entre 2026 et 2027, de plus en plus ciblés sur l’inférence en IA.

Pourquoi Meta insiste-t-elle autant sur la bande passante HBM ?

Parce que, selon la société, la bande passante de la mémoire HBM est un des facteurs clés pour la performance en inférence générative, notamment lors du décodage. C’est pourquoi la bande passante augmente fortement entre MTIA 400, 450 et 500.

Cela signifie-t-il que Nvidia perdra son importance pour les hypergéants ?

Pas nécessairement. Le mouvement vise plutôt une segmentation des usages : des puces propres à grande échelle pour l’inférence, et des GPUs toujours très présents dans l’entraînement et d’autres applications polyvalentes.

Quels autres hypergéants suivent cette stratégie ?

Google avec Ironwood TPU, AWS avec Trainium3 et Inferentia, et Microsoft avec Maia 200, également en développant leurs propres circuits spécialisés pour l’IA et l’inférence.

Sources : ai.meta.com