La société Amkor Technology a franchi une étape supplémentaire dans l’industrie des semi-conducteurs avec le développement de sa technologie d’emballage innovante S-SWIFT™. Cette nouvelle solution promet de transformer la manière dont les puces avancées sont fabriquées et connectées, en offrant des améliorations considérables en termes de performance et d’efficacité.

Le défi des nœuds plus petits

Alors que l’industrie des semi-conducteurs évolue vers des nœuds technologiques de silicium de plus en plus petits, actuellement à 3 nanomètres, les coûts et les temps de développement ont explosé. Les ingénieurs d’Amkor ont identifié que plus la taille du nœud est petite, plus le risque de défauts est élevé, ce qui résulte en des rendements inférieurs des plaquettes de silicium.

La technologie des chiplets comme solution

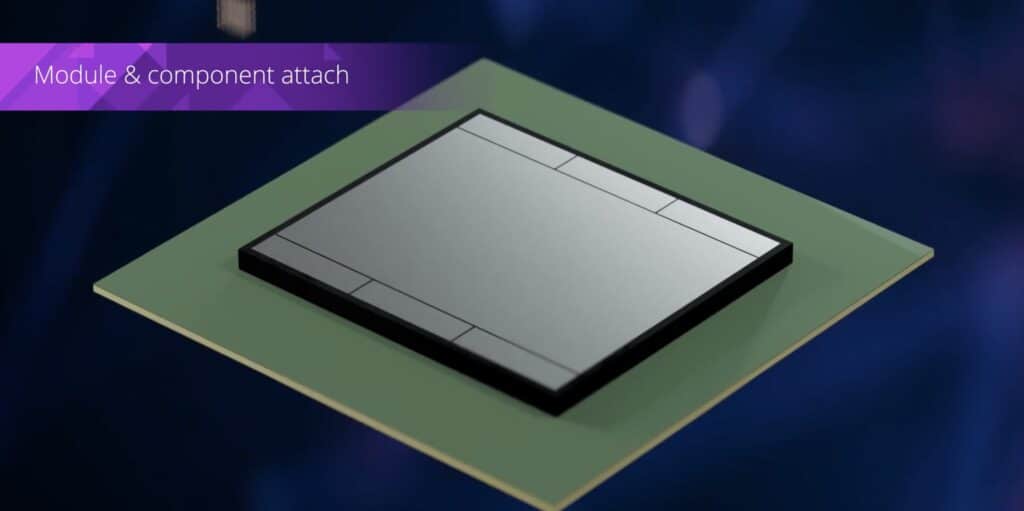

Pour répondre à ces limitations, l’industrie s’est tournée vers la technologie des chiplets. Cette approche permet de séparer les blocs centraux en puces plus petites, améliorant ainsi le rendement des plaquettes et réduisant les coûts de conception. Cependant, l’interconnexion de ces puces hétérogènes nécessite des technologies d’emballage de circuits intégrés (CI) avancées.

S-SWIFT: La réponse d’Amkor

La technologie S-SWIFT (Substrate Silicon Wafer Integrated Fan-out Technology) d’Amkor se distingue dans le paysage des emballages haute densité. Elle fournit une plus grande bande passanteLa bande passante est la capacité maximale de transfert de données… et des connexions entre puces pour une intégration hétérogène avec un interposeur de haute densité.

Caractéristiques clés de S-SWIFT:

- Interface de pitch fin et μ-bump

- Contrôle précis de la déformation pendant l’assemblage thermique

- Techniques de remplissage capillaire et de surmoulage

- Procédé de formation de boules sur le côté du moule

La technologie ETR: Le cœur de S-SWIFT

Une des innovations centrales de S-SWIFT est le processus de couche de redistribution de trace embarquée (ETR). Cette méthode aborde les défis de la fabrication de couches de redistribution (RDL) à haute densité, cruciales pour interconnecter des puces avec des blocs de nœuds plus petits.

Le processus ETR implique d’embedder la trace dans la couche diélectrique sans un processus de gravure, ce qui résout des problèmes tels que la sous-coupe de la couche de semence et les questions de gravure latérale. La structure de cuivre en damasquiné double dans le processus ETR offre des avantages dans les caractéristiques de transmission du signal haute fréquence.

Fiabilité et performance éprouvées

Les ingénieurs d’Amkor ont soumis la structure ETR dans l’emballage S-SWIFT à des tests de fiabilité rigoureux. La couche de semence qui entoure les trois faces de l’ETR agit comme une barrière, empêchant la migration des ions de cuivre et assurant la fiabilité sous des conditions de courant, de chaleur et d’humidité.

Le futur de l’emballage des circuits intégrés

Avec S-SWIFT, Amkor Technology se positionne à l’avant-garde de la technologie d’emballage de CI. Cette innovation promet de satisfaire les demandes croissantes d’applications en intelligence artificielle, en informatique haute performance et dans les centres de données.

À mesure que l’industrie continue de repousser les limites de la technologie du silicium, des innovations comme S-SWIFT joueront un rôle crucial dans la définition du futur de l’informatique haute performance.

via: amkor