La course à l’intelligence artificielle ne se résume plus à savoir qui fabrique le plus de GPU ou qui entraîne le plus gros modèle. D’ici 2026, le goulet d’étranglement de plus en plus évident réside dans la mémoire : sa bande passante, sa capacité et surtout sa disponibilité. Dans ce contexte, la Chine commence à dévoiler une stratégie qui pourrait remettre en cause la domination de la Corée du Sud dans les mémoires avancées : YMTC (Yangtze Memory Technologies) travaille sur un concept baptisé High Bandwidth Flash (HBF), une proposition visant à rapprocher la NAND 3D du calcul pour combler un vide que la HBM — essentielle dans les accélérateurs d’IA — commence à révéler.

Le principe est simple, mais il perturbe le marché : la HBM (High Bandwidth Memory) offre d’excellentes performances, mais elle est coûteuse, complexe à empaqueter et limitée en capacité totale à proximité de la GPU. Et lorsque les modèles grossissent, le problème ne se résume pas à la rapidité, mais à garder de nombreux données à proximité (poids, états intermédiaires, points de contrôle, jeux de données, historiques). C’est là que YMTC envisage que la mémoire flash pourrait jouer un rôle nouveau : non plus comme un SSD « distant », mais comme une mémoire empilée connectée avec un débit bien supérieur à celui du stockage traditionnel.

Qu’est-ce que le HBF et pourquoi devient-il au centre des discussions maintenant ?

Le HBF, tel qu’il se dessine dans l’industrie, aspire à être une mémoire flash de très grande capacité intégrée plus près du processeur ou de l’accélérateur, avec une architecture d’interconnexion conçue pour transférer des données à des vitesses supérieures à celles d’un SSD classique. Son objectif n’est pas de remplacer la HBM en termes de latence — ce serait irréaliste — mais d’offrir plus de capacité à proximité du calcul et d’alléger la pression sur le « pool » de mémoire le plus coûteux du système.

L’aspect crucial est que ce n’est pas une idée isolée ni un simple concept en laboratoire. En parallèle des initiatives chinoises, Sandisk et SK hynix ont annoncé un partenariat pour travailler à la standardisation d’une spécification de HBF, la décrivant comme une technologie adaptée aux charges de IA (notamment l’inférence) et ayant une ambition concrète : des débits comparables à la HBM et une capacité 8 à 16 fois supérieure, avec un coût « similaire » dans leur marché cible, et un calendrier visant à proposer des échantillons en 2026 et des dispositifs initiaux en 2027. Autrement dit : l’industrie cherche littéralement à « inventer » une nouvelle couche de mémoire pour l’ère de l’IA.

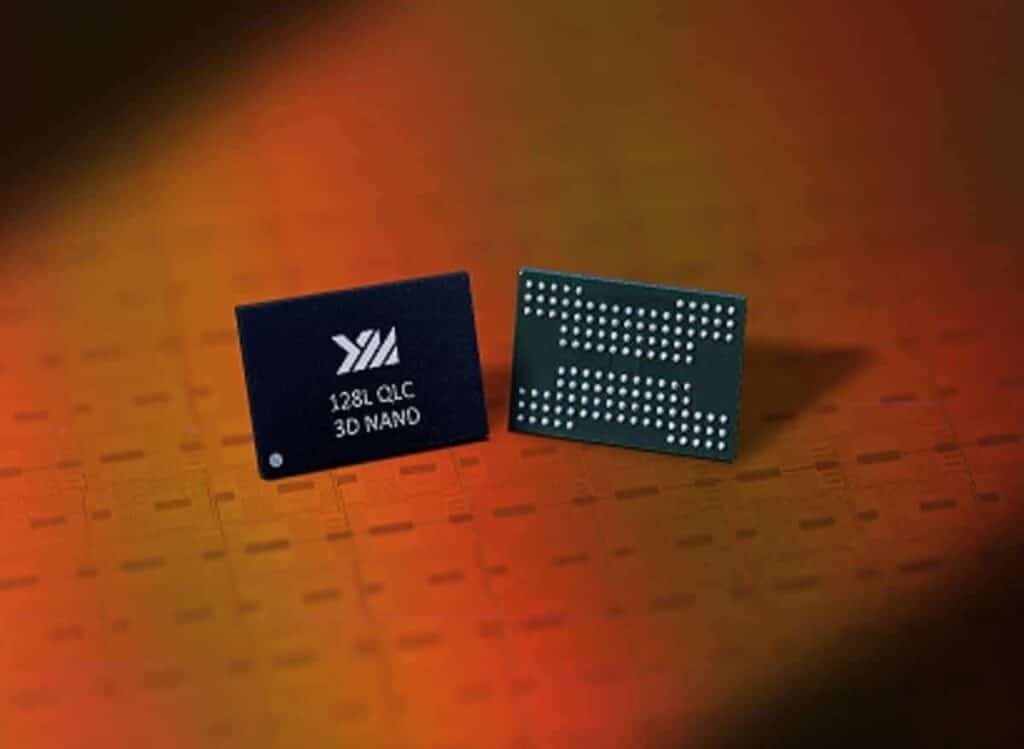

Le plan chinois : YMTC veut que la NAND cesse d’être « uniquement SSD »

Dans ce contexte, YMTC lance un mouvement stratégique. Selon des sources du marché technologique asiatique, l’entreprise a présenté des avancées dans la fabrication NAND 3D et son intention de développer le HBF, en s’appuyant sur l’évolution de sa architecture Xtacking. Celle-ci consiste à séparer la fabrication de la matrice mémoire de la partie logique et périphérique en wafers distincts, puis à les assembler via des techniques de bonding, une stratégie visant à améliorer performance et scalabilité en optimisant chaque composant séparément.

Une lecture géostratégique est évidente : YMTC agit dans un environnement marqué par des restrictions technologiques et par un objectif national de réduction de la dépendance aux semi-conducteurs étrangers. Si la Corée du Sud domine l’HBM et une grande partie des mémoires « premium » alimentant les GPU d’IA, une mémoire alternative basée sur la force de la NAND chinoise pourrait offrir une échappatoire : plus de capacité à proximité du calcul, mais avec certains compromis.

HBM vs HBF : la comparaison qui compte (et la nuance souvent oubliée)

Pour comprendre pourquoi le HBF suscite de l’intérêt, il est utile de mettre en perspective le problème :

- HBM (DRAM empilée) : excellente pour alimenter des GPU en données à haute vitesse et faible latence. C’est ce qui permet à un accélérateur d’atteindre ses performances maximales. Mais sa capacité par module est limitée, et sa production dépend d’une chaîne complexe (DRAM avancée, TSV, packaging 2.5D/3D, interposers…).

- Flash (NAND) : bon marché par gigaoctet et évolutif en capacité. Mais sa latence et sa nature de stockage en font une solution inadaptée pour remplacer la DRAM en première ligne du traitement.

Le HBF cherche à se positionner entre les deux : il ne vise pas à remplacer la RAM de la GPU, mais plutôt à offrir un niveau de stockage plus proche du processeur pour conserver plus de données sans recourir systématiquement à la coûteuse HBM. Dans un monde où chaque nouvelle version de modèles pousse à stocker davantage de points de contrôle, de versions, de résultats et d’historiques — pour la reproductibilité, la conformité ou l’audit — la nécessité n’est plus seulement de calculer rapidement, mais aussi d’avoir une mémoire et un stockage proches.

Le vrai enjeu technique est que si le HBF est mal utilisé — par exemple pour des données nécessitant une latence type DRAM — il sera un échec. En revanche, s’il est employé comme mémoire de grande capacité pour l’inférence, la mise en staging, le cache de certains actifs ou comme des couches intermédiaires, cela peut avoir un sens économique et opérationnel.

En quoi ce mouvement menace Samsung et SK hynix… même si le HBF ne remplace pas la HBM ?

Car le pouvoir ne réside pas uniquement dans la vente de HBM : il est dans le contrôle du standard de facto pour la mémoire destinée à l’IA. Si le marché accepte une architecture où une partie du « problème de capacité » se résout avec du flash empilé, la discussion change : quelle quantité de HBM faut-il vraiment à chaque nœud pour certains cas d’usage ? Quelle part du budget peut-on décaler vers une autre couche ?

YMTC voit une opportunité : la Chine ne peut pas forcément dominer la HBM de dernière génération, mais elle peut tenter de prendre une longueur d’avance avec la NAND, le bonding et l’empilement avancé. De plus, l’émergence d’un écosystème HBF — et la conversation déjà engagée entre Sandisk et SK hynix sur la standardisation — pourrait rebattre les cartes des fournisseurs.

Ce qui reste à prouver : fiabilité, logiciel, et une question cruciale

Il faut néanmoins rester humble : le HBF est une solution avec de sérieux défis. La mémoire flash vieillit, requiert une gestion sophistiquée, et ses performances dépendent fortement des contrôleurs, du firmware, et surtout de l’adaptation du logiciel d’IA à cette hiérarchie mémoire plus complexe. La réussite ne consiste pas simplement à faire un « plus grand » cartouche, mais à construire un système où il est rentable de déplacer des données vers ce nouveau niveau sans pénaliser la latence ni la consommation énergétique.

La question fondamentale est aussi simple qu’éclairante : le HBF réduira-t-il le nombre de GPU nécessaires pour une tâche donnée, ou permettra-t-il simplement d’en faire plus avec la même quantité ? Si c’est la seconde option, le marché l’adoptera car l’incitation dans l’IA est claire : évoluer en capacité.

Questions fréquentes

En quoi HBF diffère-t-il de HBM dans les centres de données d’IA ?

La HBM est une mémoire DRAM empilée avec une latence très faible et une bande passante très élevée, conçue pour alimenter la GPU en données rapidement. Le HBF vise à apporter une capacité accrue grâce à la mémoire flash, avec une bande passante élevée, mais sans remplacer la HBM pour les tâches où la latence est critique.

À quoi servirait la High Bandwidth Flash dans l’inférence de grands modèles ?

Principalement à apporter une « couche proche » de grande capacité pour gérer des modèles, des historiques et des données qui n’ont pas besoin d’être constamment en mémoire ultra-rapide, ce qui améliorerait la coût-efficacité et la scalabilité dans certains déploiements.

Le HBF peut-il réduire à court terme (2026–2027) la dépendance à la HBM ?

Il peut atténuer une partie de la pression lorsque la limitation est la capacité à proximité du calcul, mais il ne remplacera pas complètement la HBM pour une performance maximale. L’impact dépendra surtout des produits disponibles et de leur adoption par le logiciel.

Quels sont les risques d’approcher la mémoire flash d’une GPU ou d’un accélérateur d’IA ?

Le principal défi concerne la latence, la gestion de l’usure, la fiabilité, et la nécessité d’un écosystème logiciel capable de tirer parti d’une hiérarchie mémoire plus complexe sans pénaliser la performance.

Sources :