La course à la mémoire à large bande passante (HBM) entre dans une nouvelle phase. Samsung Electronics a fixé une date et un objectif pour sa prochaine avancée : HBM4E avec une cible de 3,25 TB/s et une production en volume prévue pour 2027. La société a présenté cette avancée lors du OCP Global Summit 2025 à San José, en visant une vitesse d’au moins 13 Gbps par broche et 2 048 broches d’E/S pour atteindre ce débit, ≈2,5 fois supérieur à celui de la HBM3E actuellement en circulation. L’annonce intervient après une année durant laquelle SK hynix a pris une avance avec HBM3E et s’est positionnée comme la première à produire en volume de HBM4, tandis que Micron présentait des échantillons à 11 Gbps pour sa « clientèle principale » en IA.

La lecture est claire : Samsung cherche à reprendre la tête dans la mémoire qui alimente les GPU pour IA et les accélérateurs façonnant l’industrie. La stratégie se concentre sur la vitesse et l’efficacité.

De HBM4 à HBM4E : comment en sommes-nous arrivés là ?

En janvier 2025, lors du ISSCC (San Francisco), Samsung a fixé pour HBM4 un objectif de 10 Gbps par broche — une augmentation de 25 % par rapport à l’objectif initial de 8 Gbps (soit 2 TB/s conformément au standard JEDEC). NVIDIA, principal acheteur mondial d’HBM, a demandé plus pour sa nouvelle génération d’accélérateurs Vera Rubin : plus de 10 Gbps. Samsung a réagi en montant à 11 Gbps, chiffre que SK hynix a également adopté. Micron, dont certains analystes questionnaient la capacité à atteindre cette étape, a confirmé plus tard des livraisons de 11 Gbps à un client de premier plan (en implicite, NVIDIA).

Avec HBM4 qui dépasse déjà les spécifications de base, le secteur considérait que HBM4E monterait encore d’un cran. Samsung l’a officialisé : ≥ 13 Gbps par broche, 3,25 TB/s avec 2 048 broches, et des améliorations d’efficacité énergétique supérieures au double par rapport aux 3,9 pJ/bit de la HBM3E actuelle. C’est le premier grand fabricant à fixer noir sur blanc un objectif “3 TB/s ou plus” pour la prochaine génération.

Pourquoi cela importe-t-il ? IA, bande passante et coût total de possession

La vague d’IA générative et l’entraînement de grands modèles (LLM) ont fait du débit mémoire un goulot d’étranglement. En formation, plus de TB/s signifie moins d’attente entre GPU et données ; en inférence, cela se traduit par latences moindres et un débit accru par nœud. Si de plus, la consommation énergétique par bit diminue, cela impacte directement le coût total de possession (TCO) : plus de performance par watt et un coût moindre par token à l’échelle des centres de données.

Avec HBM4E, Samsung vise cet équilibre : vitesse vertigineuse, efficacité et délais. La production en volume est programmée pour 2027, en phase avec les feuilles de route des futures GPUs.

Le contexte concurrentiel : SK hynix, Micron… et la “guerre de la vitesse”

- SK hynix a été référence en HBM3E et aspire à devenir première pour HBM4. L’annonce de Samsung cherche à forcer le rythme avec HBM4E et 3,25 TB/s, afin d’anticiper la prochaine courbe de performance.

- Micron a dissipé les doutes en confirmant des échantillons à 11 Gbps pour HBM4. Le défi pour ces trois acteurs sera de maintenir rendement et capacité à mesure que NVIDIA, et d’autres grands acteurs en hyperscale, augmentent leurs commandes.

La demande IA a bouleversé la logique traditionnelle du cycle mémoire. Au-delà de DDR5/DDR4, le capex et l’ingénierie talentueuse se concentrent désormais sur HBM — le segment avec la marge. C’est pourquoi chaque annonce de caractéristique devient aussi un message stratégique : qui mène, qui suit, et qui arrivera à temps pour la prochaine fenêtre d’intégration avec les GPU.

Ce que Samsung a annoncé : HBM4E, LPDDR6 et fonderie à 2 nm

Lors du OCP Global Summit 2025, le fabricant sud-coréen a dévoilé une panoplie complète :

- HBM4E : ≥ 13 Gbps par broche, 2 048 broches, 3,25 TB/s, avec plus du double d’efficacité énergétique (> 2×) par rapport à HBM3E. La production de masse est prévue pour 2027.

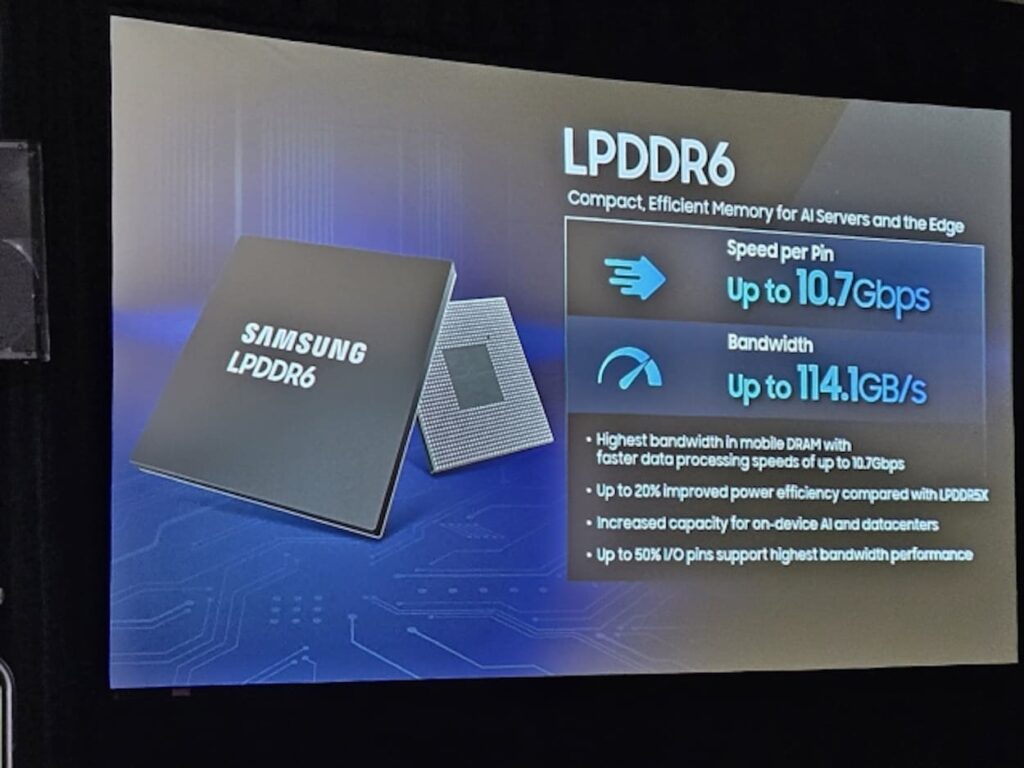

- LPDDR6 : premier produit à 10,7 Gbps par broche et 114,1 GB/s de bande passante, soit 20 % plus efficace que LPDDR5X. Cette mémoire mobile alimentera SoC et dispositifs intégrant également l’IA en périphérie.

- Fonderie à 2 nm (SF2) : en préparation et avec une mise en production prévue pour la fin de 2025. En parallèle, Samsung collabore avec Rebellions sur le Rebel Quad, intégrant une CPU ARM Neoverse V3 (“Rebel-CPU”) et une NPU fabriquées respectivement en SF2 (2 nm) et SF4X (4 nm). La fréquence cible de la CPU est entre 3,5 et 4,0 GHz, dépassant le 3,44 GHz du Grace CPU (Neoverse V2, 4 nm TSMC).

Au-delà de la simple métrique d’HBM, le message de Samsung est que toute sa chaîne —mémoire, DRAM mobile et nœuds de fabrication— est synchronisée avec la prochaine vague de produits IA-centrés.

Que signifie 3,25 TB/s… et qu’est-ce qui reste à découvrir ?

3,25 TB/s correspond à la somme de 13 Gbps par broche multipliée par 2 048 broches et convertie en octets (1 byte/8 bits). Ce chiffre n’est pas une simple valeur symbolique : il exige des interfaces, un empilement et une technologie d’interconnexion capables de gérer et de dissiper ce débit de manière fiable. Il force également à repenser les contrôleurs, la signalétique, le crosstalk et les marges dans un empilement 3D de plus en plus élevé.

Mais qu’est-ce qui reste à connaître ?

- Latences effectives et énergie par bit en silicium réel. Samsung évoque une amélioration de plus de 2× par rapport à HBM3E (3,9 pJ/bit), mais il reste à analyser les courbes de consommation selon la fréquence.

- Capacités par empilement et densités, essentielles pour l’entraînement des LLM où le “fit” du modèle dans chaque GPU fait toute la différence.

- Disponibilité coordonnée avec les GPU. Une HBM4E prête pour 2027 doit compter sur des clients clés — tels que NVIDIA, AMD, et autres — avec contrôleurs et back-ends préparés.

Il reste à voir si ces avancées seront intégrées dans le marché dans les délais annoncés, et à quel coût.

Pourquoi l’efficacité compte autant que la vitesse

Pour atteindre 3,25 TB/s, il faut dépasser 13 Gbps par broche. Chaque augmentation de vitesse accentue les défis liés au signal et à la consommation. La promesse de moins de 2× l’énergie par bit par rapport à HBM3E est donc cruciale : dégager moins de chaleur et garantir une densité accrue dans les racks avant de heurter la limite thermique. Dans un marché où la consommation et la refroidissement pèsent lourd, pJ/bit devient une métrique clé aussi critique que les Gbps.

Une nouvelle course au trône ? Ce que jouent les acteurs jusqu’en 2027

Le leadership en HBM ne se résume pas à “qui est en première ligne” ; c’est qui fournit des volumes avec performance soutenue, excellente fabrication et constante qualité. SK hynix, avec son avance en HBM3E, se positionne avec un avantage dans la course à l’HBM4. Micron a montré sa puissance avec des échantillons à 11 Gbps. Quant à Samsung, elle se distingue avec HBM4E et 3,25 TB/s comme un coup de maître pour redéfinir la carte. Le marché dira si cet objectif de bande passante se traduit en contrats importants et en capacité suffisante à temps pour les GPU en seconde moitié de la décennie.

Ce contexte montre que la compétition ne se limite pas à la vitesse, mais aussi à la capacité de fournir un produit fiable, de haute qualité, et en volume.

Et le reste du portfolio ? LPDDR6 et 2 nm aussi jouent un rôle

L’annonce de LPDDR6 (10,7 Gbps, 114,1 GB/s, +20 % d’efficacité par rapport à LPDDR5X) s’inscrit dans la diversification de la stratégie IA : mobiles, PC équipés de NPU, dispositifs en périphérie. Par ailleurs, le passage à 2 nm (SF2) rapproche Samsung du club élite recherchant fréquences et efficience de nouvelle génération. La collaboration avec Rebellions — une startup sud-coréenne en puces IA — témoigne aussi du potentiel à mixer CPU et NPU en combinant SF2 et SF4X.

Quelles attentes pour la suite ?

- Démonstrateurs et prototypes de HBM4 et HBM4E avec métriques publiques (débit soutenu, pJ/bit réel).

- Partenariats significatifs avec NVIDIA/AMD et hyperscalers pour garantir des friches de production pour 2026–2028.

- Mise à jour du jeux de standards JEDEC et de l’écosystème (contrôleurs, tests, emballages) pour soutenir la transition vers ≥ 13 Gbps par broche.

Le défi immédiat n’est plus de savoir si la HBM4E à 3 TB/s arrivera, Samsung l’a déjà confirmé. La vraie question est : qui parviendra le premier à commercialiser en volume, combien de piles par GPU seront nécessaires, et quel sera le coût énergétique par bit déplacé.

RCS Universal Profile 4.0 est désormais officiel : comment se compare au SMS, aux versions précédentes de RCS et à WhatsApp