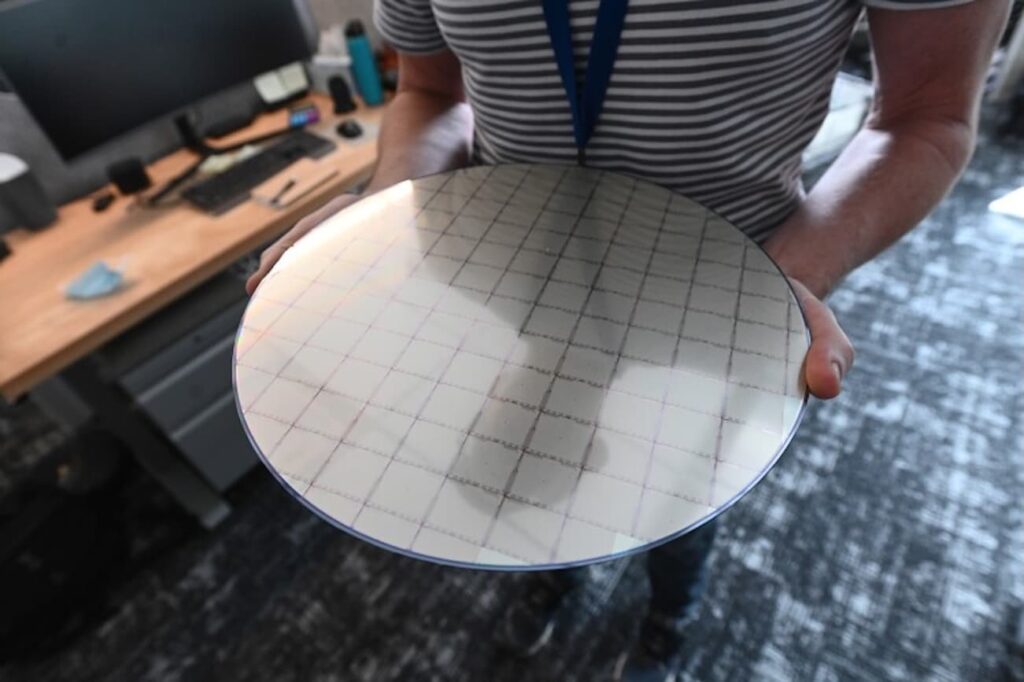

Rapidus, une entreprise japonaise innovante, a franchi une étape significative dans sa stratégie pour rivaliser avec des géants comme TSMC, Samsung et Intel. La société a lancé la production d’essai de wafers utilisant la technologie des transistors gate-all-around (GAA) à 2 nanomètres dans son usine IIM-1 au Japon. Les premières wafers produites ont déjà montré des caractéristiques électriques conformes aux attentes, signe que leur processus technologique progresse selon le calendrier prévu.

Ce développement marque une étape cruciale pour la validation que les transistors fabriqués avec cette technologie respectent des paramètres clés tels que la tension de seuil, la fuite de courant, la vitesse de commutation et la consommation énergétique. Bien que les détails précis n’aient pas été communiqués, la simple présence de wafers en production indique que l’environnement de fabrication est opérationnel.

Ce qui distingue davantage Rapidus, c’est son approche unique du traitement des wafers, privilégiant le traitement individuel pour chaque étape, contrairement à d’autres fabricants qui privilégient le traitement par lots. Cette méthode, plus coûteuse et avec une productivité potentiellement moindre par outil, permet une personnalisation en temps réel pour chaque wafer, en ajustant les paramètres selon ses caractéristiques spécifiques. Cette stratégie vise à détecter et corriger rapidement toute anomalie, tout en accumulant une grande quantité de données détaillées, exploitées via l’intelligence artificielle pour optimiser en continu le processus.

Les experts soulignent que cette architecture permet à Rapidus de s’adapter rapidement à de nouveaux designs et à des productions en faibles volumes, une nécessité pour répondre aux demandes des applications de niche, de l’intelligence artificielle et de l’informatique en périphérie. La construction de la nouvelle usine, débutée en septembre 2023, a rapidement progressé, équipée dès fin 2024 d’outils de lithographie avancés, notamment EUV, avec des premiers résultats positifs dès avril 2025.

Grâce à ces avancées, Rapidus vise à se positionner comme un acteur clé sur le marché des chips GAA, dont la demande devrait exploser avec la croissance de l’IA, du calcul haute performance et de l’informatique en périphérie. La société prévoit la disponibilité d’un kit de développement de processus (PDK) pour le premier trimestre 2026, facilitant l’accès des designers et des entreprises à leur technologie pour la conception et le prototypage.

Toutefois, cette approche innovante n’est pas sans défis. Le traitement individuel augmente la complexité opérationnelle et les coûts initiaux par chip. Pourtant, dans un contexte où chaque défaut sur des circuits à 2 nm peut représenter des pertes considérables ou des défaillances critiques, la précision prime. Selon des analystes, Rapidus semble faire le pari de privilégier le contrôle et la fiabilité plutôt que la vitesse ou le volume, une stratégie potentiellement gagnante dans un monde où l’IA change radicalement la donne.

En adoptant cette méthode, le Japon confirme son rôle de leader dans l’industrie mondiale des semi-Conducteurs, en combinant innovation, précision et autonomie technologique sur une des technologies les plus avancées de l’histoire.

Pour plus d’informations, consultez l’article sur Tom’s Hardware.