La course à l’Intelligence Artificielle en centre de données s’appuie traditionnellement sur la puissance des GPU, la vitesse des réseaux et la consommation en watts par rack. Cependant, dans la pratique, de nombreux goulots d’étranglement migrent vers un composant moins spectaculaire mais crucial : la mémoire. Micron a souhaité apporter des chiffres concrets en annonçant une avancée majeure, en ciblant directement le cœur du problème : la société commence à envoyer des échantillons à ses clients de SOCAMM2 256 Go, un module LPDRAM (LPDDR5X adaptée aux serveurs) conçu pour accélérer les architectures d’inférence et de calcul général, tout en consommant sensiblement moins que les RDIMM traditionnels.

Le contexte est essentiel : la combinaison d’ensembles d’entraînement, d’inférences, d’agents et de charges « classiques » pousse les serveurs à nécessiter toujours plus de capacité, d’efficience et de densité. Les fenêtres de contexte s’allongent, les caches KV deviennent persistantes, et le coût énergétique cesse d’être une variable annexe. Micron affirme qu’à ce niveau, la mémoire ne se limite plus à un simple accompagnement du traitement, mais devient un facteur limitant impactant performance, scalabilité et coût total de possession.

Qu’est-ce que SOCAMM2 et pourquoi cette innovation apparaît maintenant ?

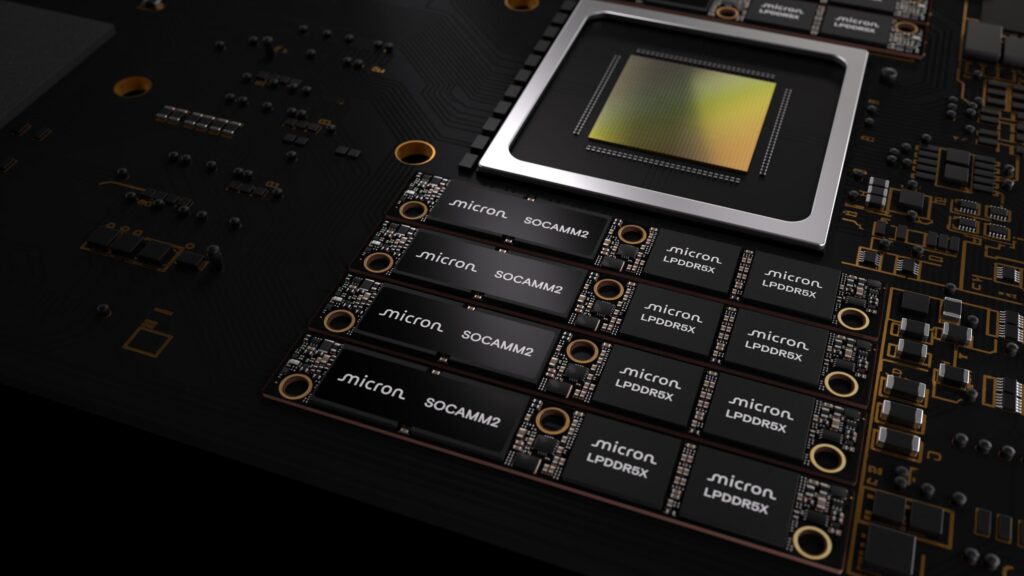

SOCAMM2 signifie Small Outline Compression Attached Memory Module 2 : un format modulaire dérivé de la famille CAMM2, conçu pour offrir une haute capacité dans un module compact et facilement remplaçable, basé sur la technologie LPDDR5X. L’ambition est d’exploiter au maximum les avantages de la mémoire à faible consommation — typique du domaine mobile —, en l’adaptant aux plateformes serveur où la densité, la gestion thermique et la consommation électrique sont des contraintes majeures.

Dans l’industrie, le SOCAMM/SOCAMM2 mûrit depuis un certain temps comme alternative pour certains designs, notamment ceux orientés vers les systèmes de haute performance et l’intelligence artificielle. Les analystes soulignent que le format 14 × 90 mm vise à réduire l’espace utilisé par rapport aux RDIMM, et que la technologie LPDDR pourrait apporter des avantages clairs en termes de consommation.

L’innovation de Micron : 256 Go, monolithe de 32 Gb, et focalisation sur l’efficacité

Le mouvement de Micron se distingue par deux avancées techniques majeures. La première : le module SOCAMM2 256 Go s’appuie sur ce que la société présente comme le premier die monolithique LPDDR5X de 32 Gb dans l’industrie. Il s’agit d’un point essentiel, car l’intégration et l’emballage font souvent la différence entre un prototype et un produit prêt à la production à grande échelle.

La seconde : Micron garantit que ce module consomme environ un tiers de l’énergie et occupe un tiers de l’espace par rapport à un RDIMM équivalent, selon une comparaison basée sur ses propres calculs (SOCAMM2 128 Go contre deux RDIMM DDR5 64 Go pour une capacité et un bus équivalents). Il faut cependant noter que cette comparaison reste indicative, dépendant de conditions et configurations spécifiques.

Ce qui rend l’annonce particulièrement disruptive, c’est l’architecture : Micron affirme qu’avec 256 Go par module, on peut atteindre 2 To de LPDRAM par CPU en configuration à 8 canaux, ciblant des environnements à grande échelle et des inférences complexes.

L’impact attendu sur l’inférence : « temps jusqu’au premier jeton » (TTFT) et cache KV

Micron met en avant une métrique clef pour le monde des grands modèles de langage (LLM) : le temps jusqu’au premier jeton (TTFT), indicateur classique de la rapidité perçue lors d’une inférence interactive. Selon ses tests internes, dans des architectures à mémoire unifiée, utiliser 2 To de LPDRAM par CPU pour décharger le cache KV peut améliorer le TTFT de plus de 2,3 fois lors de l’inférence sur de longues séquences, avec un exemple basé sur Llama 3 70B (FP16), contexte de 500K et 16 utilisateurs simultanés (données fournies par Micron).

De plus, en utilisant la mémoire de façon autonome sur CPU, Micron observe un amélioration de plus de 3 fois du rendement par watt par rapport à des modules de mémoire classiques dans certains cas HPC spécifiques.

Pour les centres de données, il ne s’agit pas uniquement d’aller plus vite, mais surtout d’être plus efficace : si une partie de l’inférence peut être maintenue avec moins de consommation électrique par GB et une densité accrue dans le rack, cela modifie radicalement le design et la gestion énergétique du datacenter — surtout dans un contexte où la fourniture électrique et la refroidissement deviennent des freins majeurs à l’expansion.

NVIDIA s’engage : co-conception et validation de plateforme

Micron présente SOCAMM2 dans le cadre d’une collaboration avec NVIDIA, visant à co-concevoir une mémoire optimisée pour l’infrastructure avancée en intelligence artificielle. L’objectif est d’optimiser « chaque couche » du système, avec l’appui d’évaluations de la part de spécialistes de NVIDIA soulignant la pertinence de combiner grande capacité et faible consommation par rapport à la mémoire traditionnelle.

Au-delà de cette collaboration, l’industrie reste attentive : pour que SOCAMM2 devienne une norme de fait, il ne suffit pas que le module existe, mais qu’il soit compatible avec des plateformes concrètes, qu’un écosystème de fournisseurs le soutienne et que la standardisation réduise les frictions entre acteurs.

JEDEC et la compétition pour établir la norme : pourquoi cela pourrait accélérer l’adoption

Micron insiste également sur sa participation à la définition de la spécification SOCAMM2 au sein de JEDEC, une étape souvent déterminante pour qu’un format passe du stade de « concept » à celui d’« option industrielle ». La création d’un standard commun permet à un nombre plus large de fabricants et d’intégrateurs de travailler sur la même base, réduisant leur dépendance aux solutions propriétaires.

Parallèlement, d’autres grands acteurs du marché ont également présenté leurs visions pour SOCAMM2 comme module LPDDR destiné aux centres de données, ce qui montre que l’industrie tend dans la même direction : plus de capacité et d’efficacité, même si cela implique de modifier les habitudes face aux RDIMM DDR5 traditionnels.

Tableau synthèse : ce que promet le SOCAMM2 256 Go de Micron

| Point clé | Ce que Micron annonce | Pourquoi c’est important pour le centre de données |

|---|---|---|

| Capacité par module | 256 Go SOCAMM2 | Plus de mémoire « proche » du CPU, idéal pour inférence et HPC |

| Die de base | LPDDR5X monolithique 32 Gb | Densité et packaging pour faire évoluer les modules |

| Capacité par CPU (8 canaux) | Jusqu’à 2 To de LPDRAM | Permet des fenêtres de contexte étendues et un cache KV plus large |

| Consommation et empreinte (comparaison) | ≈1/3 énergie, ≈1/3 espace vs RDIMM équivalent (calcul interne) | Optimise la densité dans le rack et facilite la gestion thermique |

| Performance en inférence (TTFT) | >2,3× TTFT en environnement étendu (tests internes) | Réduction du délai de réponse pour LLM interactifs |

| Performance par watt (CPU/HPC) | >3× perf/W en interne | Réduction des coûts énergétiques pour les charges utiles |

Ce qui arrive ensuite : du prototype au déploiement réel

Pour l’instant, Micron évoque uniquement la livraison « d’échantillons à ses clients ». Cette étape représente souvent le début du vrai défi : validation en plateforme, profils thermiques, compatibilité avec refroidissement liquide, support sur le terrain, et le coût par GB dans une optique commerciale. La société souligne que la modularité du design facilite la « serviceability » et supporte des architectures plus orientées vers l’efficacité énergétique.

Si SOCAMM2 256 Go parvient à s’imposer dans des produits commerciaux à l’échelle, ce ne sera pas simplement une évolution de taille : cela pourrait marquer une tendance où une partie des centres de calcul se reconfigure autour de mémoires à faible consommation, capables de soutenir une inférence à grande fenêtre tout en respectant des limites de puissance plus strictes.

Questions fréquentes

Qu’est-ce qu’un module SOCAMM2 et à quoi sert-il dans les serveurs d’intelligence artificielle ?

Il s’agit d’un format modulaire de mémoire LPDDR5X destiné aux centres de données. Son intérêt réside dans sa capacité à offrir une mémoire à haute densité et à faible consommation, adaptée aux inférences avec de larges fenêtres de contexte et des caches KV.

Pourquoi Micron insiste-t-elle sur le symbole « 2 TB par CPU » et que cela signifie concrètement ?

Micron affirme qu’avec 256 Go par module, il est possible d’atteindre 2 To de LPDRAM sur une CPU dotée de 8 canaux, permettant de stocker davantage de contexte et de réduire les goulots d’étranglement mémoire lors d’inférences complexes.

Est-ce que SOCAMM2 remplacera toutes les RDIMM DDR5 dans les centres de données ?

Pas nécessairement. SOCAMM2 cible des architectures où la consommation et la densité sont critiques. Les RDIMM resteront probablement dominants pour la majorité des applications standards, mais SOCAMM2 pourrait s’imposer pour des plateformes spécifiquement optimisées pour l’efficience.

Quels points un équipe système doit-elle surveiller avant d’adopter SOCAMM2 ?

Compatibilité avec la plateforme (CPU, carte mère), disponibilité en volume, profils thermiques, support du fabricant, et coût total par GB (en intégrant racks, alimentation et refroidissement).

Source : investors.micron