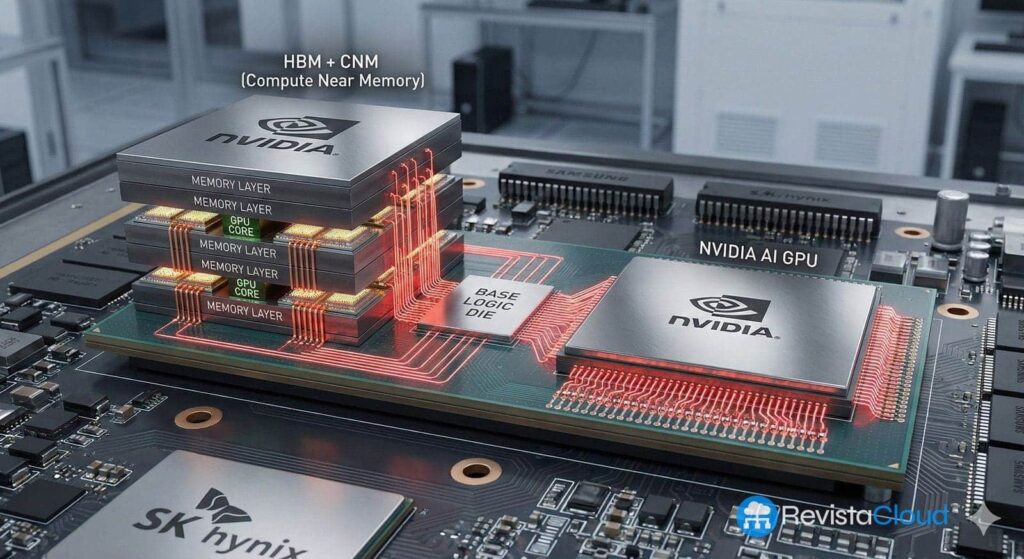

La course à la montée en puissance de l’intelligence artificielle pousse l’industrie des semi-conducteurs vers des territoires qui, il y a seulement quelques années, relevaient de la science-fiction. La dernière avancée provient de Corée du Sud : selon des sources spécialisées, Meta et NVIDIA étudient l’intégration directe de cœurs de GPU au sein de la mémoire HBM de nouvelle génération, en collaboration avec SK hynix et Samsung Electronics.

Si cette architecture venait à se concrétiser dans des produits commerciaux, cela pourrait transformer radicalement la conception des puces pour les centres de données IA et rendre la frontière entre mémoire et processeur encore plus floue.

Qu’est-ce que la HBM et pourquoi tout tourne autour d’elle

La HBM (High Bandwidth Memory) est un type de mémoire conçu pour résoudre un problème précis : le manque de bande passante entre le processeur et la RAM dans les systèmes haute performance. Plutôt que de placer les puces de mémoire autour de la GPU ou CPU, la HBM empile plusieurs couches de DRAM, superposées les unes aux autres, et les connecte via des TSV (Through-Silicon Vias), des canaux traversant le silicium verticalement.

Ces piles de mémoire sont ensuite montées sur un interposer en silicium, près du processeur, formant un assemblage dit généralement 2,5D. Le résultat est un module compact qui offre :

- Un bande passante considérablement plus élevée que la mémoire GDDR ou DDR traditionnelle.

- Une consommation d’énergie inférieure par bit transféré.

- Une empreinte physique plus réduite autour du chip principal.

Grâce à ces avantages, la HBM est devenue la mémoire de référence pour les GPU destinés à l’intelligence artificielle, les accélérateurs de calcul, et certains processeurs de haute performance. Les développements récents, tels que HBM3E et HBM4, portent cette idée encore plus loin, en augmentant le nombre de couches, le bus de communication et la fréquence, pour dépasser le seuil du téraoctet par seconde par pile mémoire.

Du contrôleur « simple » aux cœurs de GPU intégrés dans la HBM

Dans l’architecture actuelle, la HBM se limite essentiellement à stocker des données et à les fournir aussi vite que possible au processeur externe. La composante logique située en bas de la pile, appelée base die, gère principalement les communications entre les couches de mémoire et le reste du système.

Avec HBM4, un premier changement intervient : certains fabricants intègrent des contrôleurs mémoire plus avancés et une logique supplémentaire dans ce base die. Cette logique permet d’optimiser l’envoi et la réception des données, de réduire la latence et d’améliorer l’efficacité, sans toucher au noyau principal.

Ce qui est maintenant à l’étude va encore plus loin. Selon des informations provenant de Corée, Meta et NVIDIA examinent l’intégration de cœurs de GPU directement dans le base die de la HBM, transformant cette pièce en quelque chose de plus qu’un simple gestionnaire de mémoire.

Concrètement, une partie de la capacité de calcul, aujourd’hui exclusivement confiée à la GPU, pourrait être déplacée directement dans la pile mémoire. Les cœurs de GPU intégrés seraient capables d’exécuter des opérations sur les données sans besoin de les déplacer physiquement vers le processeur principal.

Pourquoi rapprocher le calcul de la mémoire peut révolutionner l’IA

Dans les grands centres de données dédiés à l’intelligence artificielle, une grande partie de la consommation énergétique et des goulots d’étranglement ne proviennent pas tant du calcul lui-même, mais du mouvement constant de données entre la mémoire et le processeur. Chaque transfert introduit une latence et une dépense en énergie.

Intégrer des cœurs de GPU dans la HBM répond précisément à ce problème :

- Réduire la distance physique entre le lieu de stockage des données et celui où elles sont traitées.

- Diminuer le trafic sur les liaisons entre la HBM et la GPU principale.

- Permettre l’exécution d’opérations simples ou répétitives directement en mémoire, laissant à la GPU centrale des tâches plus complexes.

Des sources du secteur mentionnées par la presse sud-coréenne soulignent qu’en IA, il ne s’agit plus seulement d’aller plus vite, mais aussi d’optimiser l’efficacité énergétique par opération. Réduire de quelques nanosecondes la latence et diminuer la consommation de quelques watts par accélérateur, multiplié par des dizaines de milliers de nœuds dans un centre, peut permettre des économies considérables et réduire la pression sur l’alimentation électrique.

Le défi technique : espace, énergie et chaleur dans le base die

La théorie est séduisante, mais sa mise en pratique n’est pas simple. Le base die de la HBM présente plusieurs limitations importantes :

- Le processus de fabrication avec TSV laisse peu d’espace disponible pour de la logique supplémentaire, car une grande partie de la surface est réservée aux connexions verticales entre couches de mémoire.

- Un cœur de GPU, même de petite taille, consomme de l’énergie et génère de la chaleur. Intégrer plusieurs cœurs sous une pile de DRAM pose des défis en termes d’alimentation électrique et surtout de dissipation thermique.

- Le packaging actuel en 2,5D est déjà complexe ; ajouter une logique de calcul au base die oblige à repenser le design de l’interposer, les réseaux d’alimentation, et les solutions de refroidissement.

Si les cœurs intégrés consomment trop ou chauffent excessivement, cela peut impacter négativement la mémoire, en diminuant sa fiabilité ou sa durée de vie. Le compromis entre capacité de calcul supplémentaire et stabilité du système sera un enjeu clé pour cette architecture potentielle.

Meta, NVIDIA, SK hynix et Samsung : des alliances qui transgressent les frontières traditionnelles

Le fait que les acteurs impliqués soient Meta, NVIDIA, SK hynix et Samsung Electronics illustre à quel point la carte du secteur est en train de changer. Traditionnellement :

- Les entreprises de mémoire (SK hynix, Samsung, Micron) se concentraient sur la DRAM et la NAND.

- Les sociétés de logiciel et architecture (NVIDIA, AMD, Intel, Qualcomm) concevaient GPU, CPU et SoC.

Imaginer intégrer des cœurs de GPU dans la HBM force à coordonner étroitement mémoire et logique, nécessitant une expertise avancée en foundry et en packaging. Pour la Corée du Sud, cette avancée représente une opportunité et un risque. Si SK hynix et Samsung parviennent à étendre leur rôle au-delà de la simple mémoire pour devenir des partenaires clés dans ces solutions hybrides, elles pourraient occuper une position centrale dans l’ère de l’IA.

En revanche, si elles ne parviennent pas à faire la transition vers la conception de logique ou au sein de l’écosystème “HBM sur mesure”, elles risquent de rester subordonnées aux grands fabricants de systèmes, qui utiliseraient leur capacité de production comme un simple composant dans une chaîne contrôlée de l’extérieur.

“La frontière entre mémoire et logique s’efface”

Des experts académiques du KAIST (Institut avancé de science et technologie de Corée) soulignent que la tendance est claire : la frontière entre mémoire et système s’estompe rapidement à mesure que l’IA devient plus exigeante.

Le message principal est que les fabricants de mémoire ne peuvent plus se contenter d’améliorer la densité et la vitesse ; ils doivent également investir dans la logique, proposer des solutions intégrées et participer à un écosystème comprenant la conception d’accélérateurs, le packaging avancé et le software.

Dans ce contexte, une architecture HBM avec noyaux GPU intégrés n’est pas une simple innovation isolée, mais un symptôme d’un changement d’ère : la mémoire cesse d’être un composant “passif” pour devenir un acteur actif du calcul.

HBM4, “custom HBM” et l’avenir de la computation à proximité de la mémoire

La standardisation de HBM4 et les premiers déploiements commerciaux, notamment par SK hynix et Samsung, suivent cette évolution. La nouvelle génération de HBM intègre :

- Des interfaces allant jusqu’à 2 048 bits et des vitesses dépassant le téraoctet par seconde de bande passante par pile.

- Des base dies plus complexes, capables d’intégrer des contrôleurs avancés et une logique personnalisée selon le besoin du client.

- Des techniques d’empaquetage telles que MR-MUF ou NCF+TCB, visant à améliorer l’intégrité thermique et mécanique des piles de 12 ou 16 couches.

Ce mouvement ouvre la voie à la conception de “custom HBM”, mémoires HBM4 fabriquées sur mesure pour un accélérateur spécifique, avec un base die adapté au besoin de la puce principale. Intégrer des cœurs de GPU serait alors une étape supplémentaire dans cette tendance : renforcer l’idée d’une intelligence intégrée directement dans la mémoire.

Ce que cela signifie pour l’avenir des puces IA

Si des acteurs comme Meta et NVIDIA, avec leurs partenaires mémoire, parviennent à dépasser les barrières techniques pour lancer sur le marché des HBM avec cœurs de GPU intégrés, cela pourrait entraîner des changements profonds :

- Une nouvelle catégorie d’accélérateurs : GPU ou XPU où une partie du calcul s’effectue directement en mémoire, brisant le “mur de la mémoire” qui limite actuellement de nombreux systèmes.

- Une fragmentation accrue du marché : chaque grand fournisseur de cloud pourrait demander sa propre combinaison d’accélérateur + HBM personnalisée, compliquant l’entrée de plus petits acteurs.

- Une pression renforcée sur la chaîne d’approvisionnement : nécessitant des processus logiques avancés pour les base dies, des capacités de TSV et de packaging de pointe, ainsi qu’une étroite coordination entre foundries et fabricants de mémoire.

Ces avancées consolideraient également le rôle stratégique de la HBM comme ressource clef pour l’IA, renforçant la position de quelques entreprises et pays capables de la produire à grande échelle.

Pour l’instant, l’intégration de cœurs de GPU dans la HBM reste en phase d’étude et de discussion. Néanmoins, que des acteurs de cette envergure s’y intéressent indique que la course pour briser le mur de la mémoire entre dans une phase beaucoup plus agressive.

Questions fréquemment posées sur la HBM avec cœurs de GPU intégrés

Quels seraient les avantages d’intégrer directement des cœurs de GPU dans la mémoire HBM pour l’IA ?

La principale valeur ajoutée serait de réduire le mouvement de données entre mémoire et processeur. En exécutant une partie des opérations directement dans le base die de la mémoire, on diminue la latence et la consommation d’énergie liées à ces transferts. Cela est particulièrement crucial dans les centres de données IA, où des modèles gigantesques tournent en continu, et chaque optimisation en termes d’efficacité par watt a un impact économique et opérationnel majeur.

En quoi la HBM4 avec contrôleur intégré diffère-t-elle de l’idée d’ajouter des cœurs de GPU ?

La HBM4 avec contrôleur intégré vise à optimiser la gestion des lectures et écritures, mais sa fonction principale reste le stockage et la fourniture rapides des données. Ajouter des cœurs de GPU va plus loin : cela introduit une capacité de calcul active, permettant d’effectuer des opérations directement en mémoire, sans recourir à la CPU ou GPU centrale. Ce sont deux niveaux d’intégration complémentaires : d’abord améliorer la gestion, puis ajouter la capacité de calcul.

Quels sont les défis techniques pour intégrer une GPU dans la mémoire HBM ?

Les principaux obstacles sont le espace limité dans le base die en raison des TSV, le système d’alimentation pour ces cœurs puissants, et la gestion thermique dans une pile de DRAM. Une température excessive pourrait impacter la fiabilité de la mémoire. De plus, le design du packaging et du refroidissement nécessitent de nouvelles solutions pour assurer stabilité et performance.

Comment cette tendance pourrait-elle influencer l’industrie des semi-conducteurs en Corée et à l’échelle mondiale ?

Pour des acteurs comme SK hynix et Samsung, intégrer de la logique dans la HBM représente une grande opportunité pour évoluer d’un rôle purement mémoire vers celui de partenaires clés dans le domaine de l’IA. Cependant, ceux qui ne réussiront pas à combiner mémoire, logique et packaging avancé pourraient devenir subordonnés aux grands fabricants de systèmes. À l’échelle mondiale, cette convergence renforce le caractère stratégique de la chaîne d’approvisionnement HBM et intensifie la compétition pour contrôler aussi bien la production de mémoire que celle de logique avancée.

Sources :

– Informations relayées par ETNews sur les projets de Meta et NVIDIA pour intégrer des cœurs de GPU dans le base die de la HBM, avec SK hynix et Samsung.

– Documentation technique et annonces industrielles relatives à la HBM3E et à la HBM4, par JEDEC et fabricants comme SK hynix, Samsung et Micron.

– Analyses sectorielles sur la mémoire à haut débit, le packaging 2,5D, et les tendances “compute near memory” et “compute under memory” dans les accélérateurs IA.