Le secteur de l’équipement en semiconducteurs pour la phase de back-end commence à occuper une place beaucoup plus visible dans l’industrie mondiale des puces. Selon un rapport de The Business Research Company, ce marché devrait dépasser 34 milliards de dollars d’ici 2030, avec la région Asie-Pacifique en tête et la Chine en tant que principal pays en volume prévu. Bien que ces chiffres doivent être interprétés avec prudence, puisqu’ils proviennent d’études de marché privées plutôt que de statistiques officielles auditées, ils reflètent une tendance cohérente avec le contexte actuel de l’industrie : l’assemblage, le conditionnement et les tests finaux sont devenus des étapes critiques pour la fabrication de puces de plus en plus complexes.

La véritable évolution ne réside pas seulement dans la quantité produite, mais dans la qualité. La vague de demande induite par l’Intelligence Artificielle, la mémoire HBM, le calcul haute performance et les architectures basées sur les chiplets a poussé toute la chaîne de valeur à accorder une attention accrue à la phase finale du processus. Selon SEMI, le segment du back-end devrait continuer à croître en 2026, avec une augmentation de 12,0 % pour les tests et de 9,2 % pour l’assemblage et le conditionnement, en raison de la complexité accrue des architectures et des exigences de performance pour l’IA et la mémoire HBM.

De l’encapsulation classique au conditionnement avancé

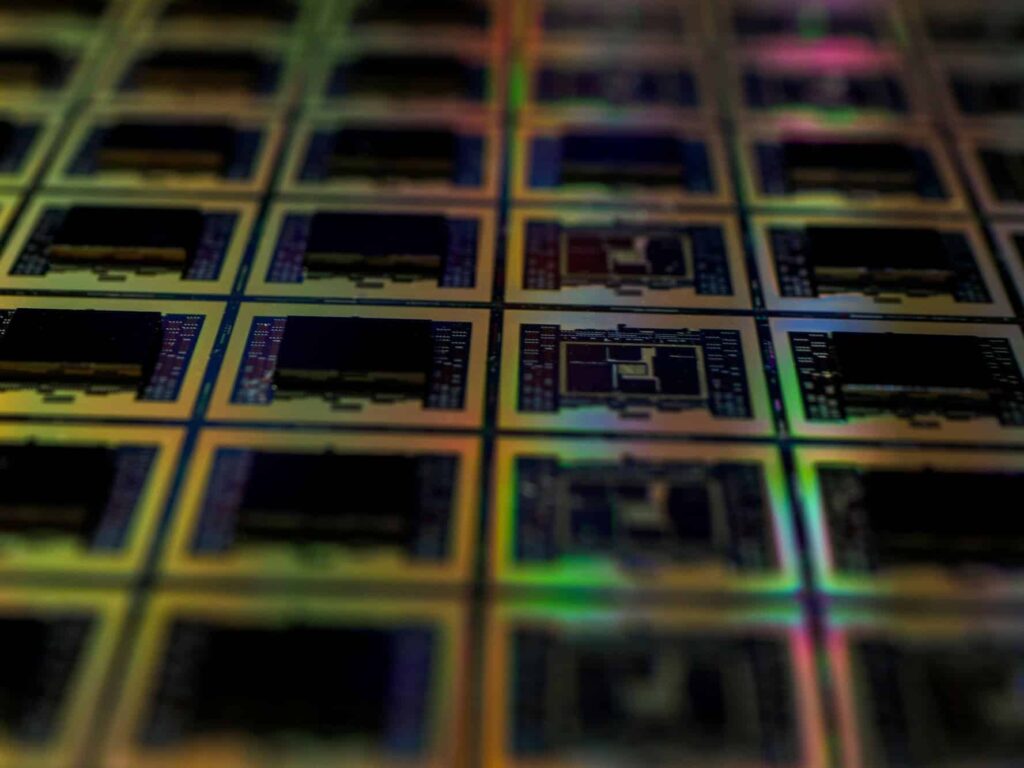

Quand on parle de back-end, on fait référence, en termes généraux, à la dernière étape de la fabrication des semiconducteurs : préparation du wafer, collage du die, wire bonding, encapsulage, assemblage et tests. Il ne s’agit pas d’une étape secondaire ou purement logistique. C’est à cette étape que se jouent une grande partie de la fiabilité, la dissipation thermique, la consommation d’énergie, l’intégration avec la mémoire ou les substrats avancés, ainsi que le rendement réel une fois le produit commercialisé. Les descriptions commerciales du secteur répartissent généralement ce marché en quatre grandes parties : le die bonding, le wire bonding, le packaging et les systèmes de test.

Ce changement de poids industriel se manifeste clairement dans la stratégie des grands fabricants. TSMC insiste depuis des années sur le fait que la valeur ne réside plus uniquement dans le nœud de fabrication, mais aussi dans la capacité à intégrer plusieurs puces en tant que système. Sa plateforme 3DFabric regroupe des technologies telles que SoIC, CoWoS et InFO, qu’elle présente comme une combinaison de technologies front-end et back-end, visant à résoudre les problèmes d’intégration hétérogène et à accélérer le passage à la production de masse. En d’autres termes, le conditionnement est passé du simple « dernier stade » à un véritable levier concurrentiel.

Les résultats de plusieurs entreprises spécialisées confirment cette tendance. ASMPT a annoncé des revenus de 532,1 millions de dollars dans son activité d’emballage avancé en 2025, en hausse de 30,2 % par rapport à l’année précédente, notamment grâce à ses solutions TCB. Besi, l’un des noms les plus suivis dans ce domaine, a révisé à la hausse ses prévisions financières à long terme en 2025, anticipant une demande accrue pour le conditionnement avancé dans la logique et la mémoire. Enfin, Teradyne a clôturé le quatrième trimestre 2025 avec 883 millions de dollars de revenus issus du secteur du test des semi-conducteurs, sur un total de 1 083 millions, soutenu par la demande liée à l’IA dans la computation, les réseaux et la mémoire. Ces mouvements ne sont pas isolés : ils illustrent que le goulet d’étranglement dans la fabrication des puces ne concerne plus seulement la tranche de silicium, mais aussi la façon dont elles sont emballées et validées.

L’Asie concentre les investissements, la Chine donne le rythme

Le rapport publié cette semaine indique que la région Asie-Pacifique pourrait atteindre 17 milliards de dollars en 2030 dans ce secteur, la Chine représentant à elle seule environ 10 milliards. Cette prévision s’accorde avec la réalité géographique du secteur : c’est en Asie que se concentre une part importante des capacités d’assemblage, de test et de packaging, où opèrent de nombreux grands OSAT et fabricants disposant d’une forte industrie. C’est également là que l’on observe le plus clair impact des aides publiques, de la pression pour l’autosuffisance technologique, et de l’expansion des capacités de production.

Les données de SEMI confirment cette tendance, même si elles ne couvrent pas exactement le même sous-segment. L’association prévoit que la Chine, Taiwan et la Corée du Sud continueront d’être les principaux marchés pour l’équipement en semi-conducteurs jusqu’en 2027. À Taiwan, une partie de cette croissance est toujours liée à la capacité de pointe dans l’IA et le calcul haute performance. En Chine, le poids reste considérable, malgré une modération attendue après plusieurs années d’investissements très agressifs. Cette synergie explique en partie pourquoi le back-end prend autant d’ampleur : il ne s’agit pas seulement d’ouvrir de nouvelles usines, mais aussi de disposer de machines capables d’assembler, d’encapsuler et de tester des puces de plus en plus exigeantes.

Un marché en croissance, mais avec des prévisions à nuancer

Cependant, il est important de ne pas considérer ces chiffres comme une vérité absolue. Une autre étude commerciale, publiée par ResearchAndMarkets, présente un scénario plus prudente : 23,54 milliards de dollars en 2026 et 32,76 milliards en 2030. Bien que ces chiffres restent alignés avec la tendance globale, ils rappellent que les méthodologies, définitions et périmètres diffèrent d’un rapport à l’autre. Dans un secteur aussi spécialisé, une différence dans la façon dont chaque entreprise définit « équipement de back-end » peut représenter des milliards de dollars d’écart apparent.

L’essentiel, au-delà des chiffres précis, réside dans le message industriel : la phase finale du processus de fabrication des puces ne peut plus être considérée comme une activité secondaire ou à faible valeur ajoutée. L’expansion de l’Intelligence Artificielle, la mémoire avancée, les chiplets, ainsi que le conditionnement en 2,5D et 3D, redirigent les investissements vers les machines qui assemblent, encapsulent, connectent et testent ces composants. Bien que le marché du back-end reste plus modeste que celui de l’équipement front-end, il devient de plus en plus stratégique pour déterminer quelles entreprises pourront augmenter leur production, améliorer le rendement et capturer de la valeur dans la nouvelle course aux semi-conducteurs.

Questions fréquentes

Que signifie back-end dans la fabrication de puces ?

Il s’agit de la dernière étape du processus de fabrication des semi-conducteurs, où le wafer est découpe, le die est associé au substrat ou à l’encapsulation, connecté, protégé et testé avant la commercialisation. Inclut l’équipement de die bonding, wire bonding, emballage et test.

Pourquoi le conditionnement avancé sera-t-il si crucial en 2026 ?

Parce que les puces destinées à l’Intelligence Artificielle, la mémoire HBM et le calcul haute performance nécessitent une intégration de plusieurs dies, mémoire et substrats avancés avec une densité accrue, une meilleure gestion thermique et des bandes passantes élargies. TSMC, notamment, met en avant ses technologies CoWoS, InFO et SoIC comme composantes clés de cette évolution.

Quelles entreprises bénéficient le plus de la croissance du back-end ?

Les fabricants d’équipements d’assemblage, de packaging et de test comme ASMPT, Besi et Teradyne sont parmi les plus exposés. Leurs résultats récents indiquent une forte demande pour des solutions liées au conditionnement avancé et au test de puces pour l’IA.

L’Asie continuera-t-elle à dominer ce secteur dans les prochaines années ?

Tout indique que oui. Les analyses prévoient que l’Asie-Pacifique reste la région leader, avec la Chine, Taiwan et la Corée du Sud en tête des investissements en équipement semi-conducteur jusqu’à au moins 2027.

via : semiconductors news