FuriosaAI Introduit une Nouvelle Architecture de Chip d’IA: Le Traitement de Contraction de Tenseur

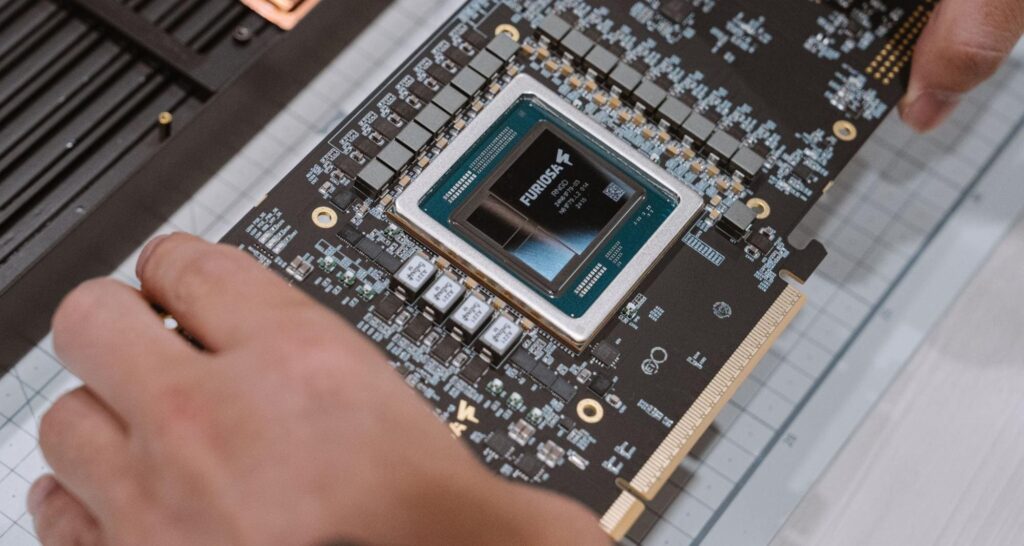

Alors que les applications d’intelligence artificielle (IA) deviennent de plus en plus complexes, les entreprises cherchent des architectures matérielles plus efficaces et évolutives pour exécuter des modèles d’apprentissage profond. La société émergente FuriosaAI, spécialisée dans le développement de chip d’IA, a récemment lancé le Traitement de Contraction de Tenseur (TCP) en tant qu’alternative aux matrices systoliques traditionnelles.

Mais est-ce que le TCP représente une véritable innovation ou est-ce simplement une évolution des architectures existantes ? Pour répondre à cette question, les ingénieurs de FuriosaAI, Younggeun Choi et Junyoung Park, ont récemment présenté les différences entre le TCP et les matrices systoliques lors d’événements majeurs tels que la Hot Chips Conference, le AI Hardware Summit et la PyTorch Conference.

Voici un aperçu de leurs explications et de la façon dont le TCP pourrait redéfinir l’accélération de l’IA.

Qu’est-ce qu’une matrice systolique et quelles sont ses limites ?

Une matrice systolique est une grille d’éléments de traitement (PEs) qui déplace les données de manière structurée et synchronisée, un peu comme le rythme d’un cœur (d’où le nom "systolique"). Elle est largement utilisée pour la multiplication de matrices, une opération clé en apprentissage profond, et a constitué la base de nombreux accélérateurs d’IA.

Bien que les matrices systoliques offrent une haute efficacité et un faible consommation d’énergie à des conditions optimales, leur structure rigide présente plusieurs limitations, notamment : un taille fixe qui gaspille des ressources, un modèle de flux de données prédéfini qui limite l’adaptabilité pour différents formats de tenseurs, et un risque d’inefficacité en fonction de la taille de la matrice.

C’est ici que l’architecture TCP de FuriosaAI espère faire la différence.

Qu’est-ce qui rend le TCP différent ?

Bien que le TCP et les matrices systoliques visent tous deux à paralléliser les calculs, FuriosaAI introduit des innovations clés en matière de flexibilité et d’efficacité :

-

Configuration dynamique des unités de calcul: Contrairement à la structure fixe des matrices systoliques, les unités de TCP, appelées « slices », peuvent être reconfigurées selon la taille du tenseur, permettant une haute utilisation même avec des charges de travail de tailles variables.

-

Flexibilité accrue dans le mouvement des données: Alors que les données dans une matrice systolique se déplacent dans une seule direction, le TCP utilise un réseau de recherche pour distribuer les données à plusieurs unités de traitement simultanément, augmentant ainsi la réutilisation des données.

-

Opérations tensoriales natives: Le TCP traite les tenseurs directement, évitant la nécessité de conversions inefficaces, ce qui simplifie l’optimisation de nouveaux modèles d’IA, comme les modèles Llama 2 et Llama 3.

- Efficacité énergétique améliorée: Le TCP maximise la réutilisation des données en interne, réduisant ainsi les accès coûteux à la mémoire externe, ce qui représente un immense gaspillage d’énergie.

TCP face aux défis des charges dynamiques d’IA

Le TCP se distingue par sa capacité à gérer les tailles de lots et formes de tenseurs variables, grâce à sa reconfiguration dynamique. Cela le rend idéal pour les modèles d’IA de grande envergure utilisés par des prestataires d’IA dans le cloud et de grandes entreprises.

TCP vs GPUs: Améliorations en matière d’inférence d’IA

Les GPUs dominent actuellement le secteur de l’accélération de l’IA, mais elles présentent certaines inefficacités par rapport aux chips comme le TCP :

-

Consommation d’énergie: Les GPUs peuvent consommer jusqu’à 1 200 W, tandis que le chip RNGD de FuriosaAI ne consomme que 150 W, offrant ainsi une réduction significative.

-

Traitement efficace des données: Les GPUs traitent les tenseurs comme des matrices 2D, ajoutant une surcharge qui réduit le parallélisme, tandis que le TCP conserve les structures tensoriales sans transformations inefficaces.

- Déploiement et personnalisation des modèles: Optimiser un modèle pour une GPU nécessite des efforts d’ingénierie considérables, ce qui est simplifié par le TCP.

L’avenir de l’accélération de l’IA : Quelle place pour le TCP ?

Le secteur des chips d’IA est en évolution rapide avec une demande croissante pour des chips personnalisés, suggérant un déclin des chips d’IA à usage général. Le TCP s’inscrit parfaitement dans cette tendance, représentant une évolution par rapport aux matrices systoliques.

Conclusion: TCP, futur du hardware d’IA ?

L’architecture TCP de FuriosaAI marque un avancement significatif dans l’accélération de l’IA, atténuant les limitations souvent rencontrées avec les matrices systoliques et les GPUs. Avec des entreprises comme Meta s’intéressant aux acquisitions dans ce domaine, le TCP pourrait jouer un rôle crucial dans la prochaine génération de matériel d’IA.

Source : FuriosaAI