La course à la fabrication de puces plus grandes et de meilleure qualité ne se limite plus à la simple conception du modèle le plus imposant, mais devient une compétition beaucoup plus tangible : combien d’outils sont installés dans les usines, combien de lignes sont automatisées et quelle capacité réelle est mise en production. Ce « thermomètre » — la vente mondiale d’équipements pour semi-conducteurs — atteint des sommets historiques.

Selon les prévisions présentées par SEMI lors de Semicon Japan, les ventes mondiales d’équipements de fabrication de semi-conducteurs connaîtront une croissance de 13,7 % en 2025, atteignant un record de 133 milliards de dollars. Et si le cycle ne se brise pas, cette tendance devrait se poursuivre en 2026 (145 milliards) et 2027 (156 milliards), enchaînant trois années d’expansion dans un secteur où les courbes sont souvent plus sinueuses qu’il n’y paraît.

IA, certes… mais aussi des “usines qui se reconstruisent de l’intérieur”

Le récit dominant reste centré sur l’IA, car elle entraîne une rénovation agressive du parc industriel : des nœuds de logique avancés, DRAM et surtout mémoire HBM pour alimenter les accélérateurs. Mais l’aspect clé de cette phase du cycle, c’est que la croissance ne se limite pas à “plus de GPU” : des investissements importants sont aussi consacrés à l’assemblage, au test et à l’empaquetage de puces de plus en plus complexes.

Concrètement, l’industrie injecte de l’argent sur trois fronts simultanément :

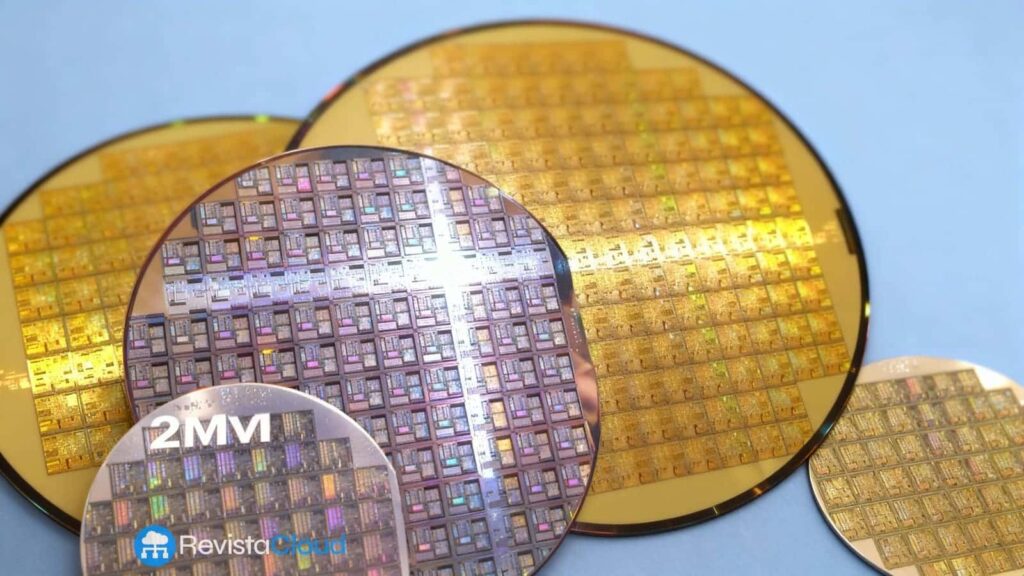

- Front-end : outils pour les galettes (lithographie, dépôt, gravure, métrologie) destinés aux nœuds avancés.

- Back-end : équipements de test et assemblage/empaquetage, devenus essentiels pour la performance finale et la consommation d’énergie.

- Intégration hétérogène : “colle” industrielle permettant de combiner chiplets, mémoire et accélérateurs en un seul produit, sans faire exploser les coûts ni la latence.

Le front-end domine… mais le back-end réalise un saut peu habituel

Dans l’ensemble, SEMI prévoit que l’investissement en équipements pour usines de wafers (WFE) atteindra 115,7 milliards de dollars en 2025, soit une hausse de 11 % par rapport à l’année précédente. C’est cette partie qui capte l’attention, car c’est là que se décide la capacité de fabrication pour les nœuds avancés.

Cependant, le fait le plus frappant — par sa rapidité, non par son volume — concerne le back-end. SEMI anticipe qu’en 2025 :

- Le matériel de test croîtra de 48,1 %, pour atteindre 11,2 milliards de dollars.

- Le matériel d’assemblage et d’empaquetage augmentera de 19,6 %, pour atteindre 6,4 milliards de dollars.

En d’autres termes : on ne se contente pas de produire plus de puces, mais on investit massivement pour les vérifier plus rapidement, les classer avec précision et les empaqueter de façon que, il y a quelques années, cela relevait presque de l’artisanat de laboratoire alors qu’aujourd’hui, c’est une production industrielle.

2 nm, GAA et le retour du “chip difficile”

Les prévisions s’accordent aussi avec la carte technologique anticipée pour 2026-2027 : la transition vers des nœuds de 2 nm avec architectures GAAF (Gate-All-Around) et la consolidation de l’intégration hétérogène comme norme, et non comme exception.

Concrètement, cela signifie qu’au fur et à mesure que la miniaturisation des transistors devient plus coûteuse et complexe, l’utilisation de chiplets et d’intégration hétérogène s’intensifie. Le packaging ne se contente plus d’un rôle d’enveloppe, mais devient une partie intégrante de la performance et de la conception du système.

L’effet “chaîne” : quand le goulot change de place

Ce cycle illustre aussi une réalité complexe : le goulot d’étranglement se déplace. Si une organisation investit dans le front-end mais néglige les tests et l’empaquetage, elle accumule de la valeur “à mi-chemin”. Si, au contraire, elle accélère l’empaquetage sans disposer de suffisamment d’objets en wafers, le capital est sous-utilisé.

Les prévisions montrent ainsi une croissance soutenue et équilibrée : l’IA pousse fortement, oui, mais le marché apprend que le produit final dépend de l’ensemble de la chaîne, et que le back-end n’est plus simplement la “dernière étape” mais une partie intégrante de la stratégie de performance.

Un marché plus vaste… et plus géopolitique

Parallèlement, l’investissement dans les équipements est indissociable du contexte géopolitique. Déjà en 2025, Reuters soulignait que cet investissement demeure fortement influencé par des stratégies nationales, des restrictions technologiques et des objectifs d’autosuffisance, avec une forte domination asiatique dans les dépenses.

Cela ajoute une nouvelle dimension à la pression : l’équipement n’est pas seulement une décision industrielle, c’est aussi une décision stratégique qui détermine quels pays et quelles entreprises peuvent fabriquer quoi, et à quel moment.

Questions fréquentes

Que signifie le fait que les ventes d’équipements pour semi-conducteurs atteignent 133 milliards de dollars ?

Que les usines (fabs) et les lignes d’assemblage achètent de la machinerie à un rythme record : plus de capacité, plus d’automatisation et davantage d’outils pour les nœuds avancés et l’empaquetage.

Pourquoi le marché du test de puces progresse-t-il autant en 2025 ?

Parce que les puces pour l’IA, notamment avec HBM et emballages complexes, nécessitent plus de tests, de rapidité et de précision pour maintenir le rendement et respecter les objectifs de latence, consommation et fiabilité.

Qu’est-ce que le wafer fab equipment (WFE) et pourquoi représente-t-il autant de dépense ?

Il inclut tous les outils pour traiter les wafers (lithographie, dépôt, gravure, métrologie, etc.), savoir quelle capacité est réellement disponible pour produire sur les nœuds avancés et, par conséquent, définir le plafond industriel.

Quel lien entre 2 nm (GAA) et l’essor du packaging avancé ?

Car à mesure que la miniaturisation devient plus coûteuse et complexe, l’utilisation de chiplets et d’intégration hétérogène augmente. Le packaging ne se résume plus à un simple emballage, mais devient une partie essentielle de la performance et de la conception du système.

Source : SEMI (chiffres liés au back-end : test et assemblage/empaquetage)