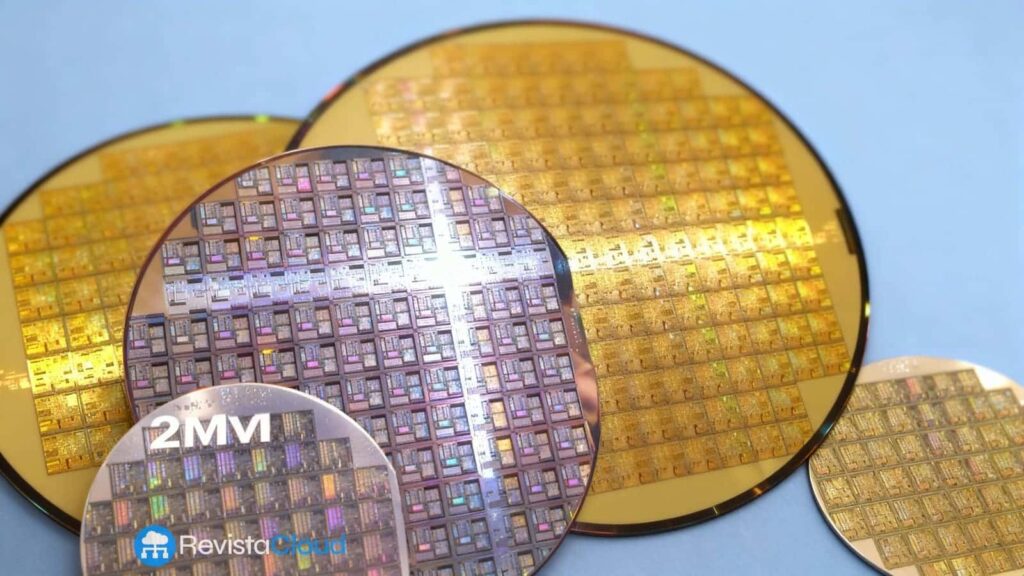

La prochaine grande bataille dans l’industrie des semi-conducteurs ne se jouera pas uniquement sur les benchmarks ou dans les nouvelles générations de GPU. Elle se déroulera surtout —dans une file d’attente de production—. Avec le passage aux 2 nanomètres, la capacité de fabrication devient une ressource stratégique : ceux qui réussiront à réserver des wafers à temps auront l’avantage pour lancer des accélérateurs d’intelligence artificielle plus performants ; ceux qui arriveront en retard risquent de se voir exclus de la conversation.

Au cœur de cette compétition se trouve TSMC, la grande fonderie qui produit pour une grande partie du marché mondial. L’industrie ne cesse d’alerter sur le fait que la demande pour ces nœuds avancés dépasse largement l’offre, et la direction de TSMC elle-même a reconnu que sa capacité « est limitée » face à l’appétit de ses principaux clients en calcul avancé.

Une nouvelle ère : du FinFET au GAAFET, et du « plus rapide » au « plus efficace »

Le nœud de 2 nm ne se contente pas d’une simple évolution incrémentielle. Il marque une rupture technologique, notamment grâce à l’intégration de transistors de type GAAFET/nanosheet qui cherchent à optimiser trois variables simultanément : performance, consommation et densité. Dans un contexte où la facture énergétique du calcul pèse déjà lourd dans les budgets et où les limites physiques des data centers restent un défi, l’efficacité énergétique devient aussi critique que la puissance brute.

Les signaux indiquant que ce nœud « va sérieux » proviennent aussi d’indicateurs techniques : des analyses de suivi de l’industrie ont identifié des améliorations dans des métriques telles que la densité de défauts en phases comparables de maturité face aux générations précédentes, un paramètre clé car il influence le rendement par wafer et, en définitive, le coût réel de chaque puce.

Qui sera le premier à adopter le 2 nm ? Les mobiles d’abord, puis l’IA

En pratique, le lancement d’un nœud de pointe est généralement piloté par le calendrier des grands fabricants de téléphones (volume, prévisibilité, cycles annuels). Mais l’IA a changé la donne : les grands accélérateurs et ASIC pour entraînement et inférence sont en train de stimuler la demande en capacité avancée avec une intensité sans précédent.

Des médias spécialisés asiatiques décrivent un risque de capacité très tendue pour le 2 nm, en raison de réservations importantes de clients de premier plan, avec une tension croissante entre le marché mobile et celui de haute performance.

Par ailleurs, d’autres publications mentionnent la forte progression du nœud N2, ainsi que son calendrier d’entrée en production, dans un contexte où l’industrie considère que l’IA continuera d’absorber une part croissante du marché.

Idée clé : le 2 nm n’est pas seulement une avancée technique ; c’est aussi un point de congestion commerciale. Et dans un marché où lancer trop tard peut coûter des contrats millions, la priorité est de sécuriser sa place.

Tableau 1 — Ce que l’on sait du saut vers le 2 nm et pourquoi cela compte

| Élément | Ce qui change | Pourquoi c’est crucial pour l’IA |

|---|---|---|

| Nœud 2 nm (N2) | Transistors GAAFET/nanosheet | Meilleure efficacité énergétique par opération ; densité accrue pour intégrer logiques et contrôles |

| Calendrier industriel | Montée en puissance progressive de la production et adoption par étapes | Les grands lancements dépendent de réservations anticipées de capacité |

| Coût par puce | Varie selon le rendement par wafer (yield) | Si le yield met du temps à se stabiliser, les puces « stars » deviennent plus chères ou retardées |

| Autre goulot d’étranglement | Emballage avancé (chiplets, interposers) | On peut avoir des wafers… mais ne pas pouvoir les empqueter à la cadence nécessaire |

L’autre grand frein : le packaging avancé

Même si le monde disposait d’un surplus de wafers, un autre problème persisterait : comment transformer ces morceaux de silicium en systèmes « gigantesques » prêts pour l’IA. Les accélérateurs modernes ne sont plus « une seule puce » : ils consistent en regroupements de chiplets, mémoires et liaisons haute vitesse intégrés dans des empaquetages de plus en plus complexes.

Les technologies de packaging avancé — telles que CoWoS et ses variantes — deviennent ainsi un second goulet d’étranglement. Le marché considère que ces limitations ne seront pas levées du jour au lendemain, et plusieurs analyses estiment que la tension en capacité d’emballage pourrait perdurer jusqu’en 2025–2026.

En langage simple : il ne suffit pas d’avoir « le meilleur nœud » ; il faut aussi maîtriser packaging + mémoire + énergie. Et tout cela doit arriver à temps.

Tableau 2 — Les grands acteurs et leur principal type de demande

| Type d’acteur | Ce qu’ils recherchent | Les pressions sur la chaîne d’approvisionnement |

|---|---|---|

| Chips mobiles (volume élevé) | Optimisation maximum en efficacité par watt et maîtrise des coûts | Capacité stable et montée en cadence prévisible |

| GPU pour IA (haute performance) | Performance, efficacité et évolutivité | Oblettes avancées + empaquetage de grande taille |

| ASIC pour hyperscalaires | Intégration optimisée pour des charges spécifiques | Réservations longues de capacité et gestion des coûts |

Ce que cela signifie pour l’utilisateur « lambda »

Bien que le débat semble éloigné, ses effets se manifestent concrètement de plusieurs façons :

- Prix : si la capacité est limitée, le coût se reportera sur le matériel, les services cloud et, en cascade, sur les produits finis.

- Disponibilité : les lancements dépendent de fenêtres de fabrication ; si celles-ci se rétrécissent, cela provoquera des retards ou des quantités moindres.

- Efficacité énergétique : les nœuds plus avancés aident à réduire la consommation par opération, un enjeu critique dans la stratégie économique de l’IA.

Il y a aussi un aspect géopolitique inévitable : quand une ressource industrielle devient stratégique, les États et entreprises ajustent leurs plans d’investissement, de localisation et de sécurisation des approvisionnements. Dans ce contexte, Taïwan occupe une place centrale… et l’Espagne le perçoit indirectement via les coûts, projets de centres de données et accès à la technologie dans l’économie numérique.

Questions fréquentes

« 2 nm » signifie-t-il que les transistors mesurent littéralement 2 nanomètres ?

Pas exactement. Le « nm » moderne est davantage un nom de génération qu’une mesure physique directe. Cependant, cela implique généralement des améliorations concrètes en densité, consommation et performance.

Pourquoi le packaging avancé est-il aussi crucial que le nœud ?

Parce que les puces IA actuelles dépendent énormément de chiplets et mémoires dans des configurations massives. Sans une capacité de packaging à grande échelle, impossible d’expédier des produits, même si les wafers existent.

Quand observera-t-on cet impact dans les produits et services ?

Les effets se font d’abord sentir dans l’infrastructure et les centres de données, puis dans les dispositifs et services. Pour le consommateur, cela signifie souvent une meilleure performance/prix dans le hardware et des coûts plus faibles pour les services.

Existe-t-il des alternatives si la capacité en 2 nm ne se concrétise pas ?

Il y a d’autres fonderies, ainsi que des stratégies comme l’optimisation architecturale, le recours aux chiplets ou des nœuds « affinés ». Cependant, pour certains volumes et exigences de performance, la dépendance à la capacité de pointe demeure forte.

source : ctee.com.tw