Depuis près de 60 ans, la Loi de Moore demeure la boussole de l’industrie : tous les 18 à 24 mois, davantage de transistors par puce, offrant ainsi plus de puissance pour chaque euro dépensé et pour chaque watt consommé. Cependant, ce cycle vertueux rencontre aujourd’hui un mur physique. À l’échelle de quelques nanomètres, les effets quantiques, les courants de fuite et la densité thermique transforment la processus de miniaturisation du silicium en un jeu à rendements décroissants. Le résultat est évident : frequences plafonnant autour de 5 GHz, gains de performance de plus en plus modestes par nœud, et une escalade des coûts et complexités qui ne peut être soutenue que par quelques usines de pointe.

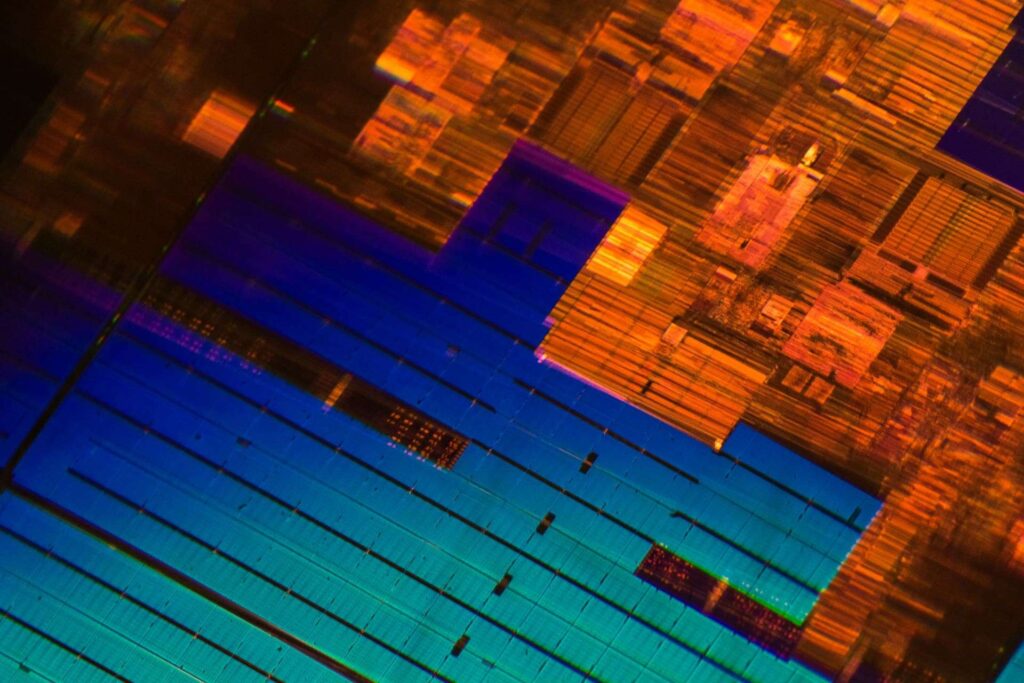

Parallèlement, alors que l’Occident affine les FinFETs et GAAFETs en silicium, poussant la packagerie 3D pour des applications telles que la mémoire HBM ou les emballages avancés, une équipe de l’Université de Pékin a proposé une alternative innovante : transistors gate-all-around (GAA) à deux dimensions basés sur le bismuth, intégrés monolithiquement en 3D à basse température. Leur étude, publiée dans Nature Materials, met en lumière une paire de matériaux qui semblent faits pour s’entendre : Bi₂O₂Se comme semiconducteur canal et Bi₂SeO₅ comme dieléctrico de puerta. L’objectif n’est pas simplement « optimiser encore le silicium », mais plutôt changer de voie : utiliser 2D + GAA + 3D épitaxial pour réduire la tension électrique, mieux contrôler le canal, et surtout superposer des fonctionnalités sans endommager la couche inférieure.

Voici l’essentiel de cette approche, l’intérêt qu’elle présente, et les défis restant à relever avant sa commercialisation.

Pourquoi le silicium approche de ses limites (et pourquoi « le faire plus petit » ne suffit pas)

Dans un transistor nanométrique, les électrons ne suivent plus la physique macroscopique classique. Le tunnel quantique à travers la diélectrique devient significatif ; les fugues d’électricité persistent même lorsque le transistor est éteint ; et la puissance par unité de surface atteint des niveaux difficiles à dissiper. Modifier la géométrie — de planar à FinFET puis à GAAFET (où la porte entoure le canal « de toutes parts ») — a permis d’améliorer le contrôle électrostatique, de contenir les fuites et de prolonger l’échelle. Mais le matériau de base, si avec SiO₂ ou d’autres oxydes à haute constante diélectrique déposés par-dessus, invoque toujours ses restrictions : interfaces trapant, constantes diélectriques qui imposent des épaisseurs minimales, températures de procédé incompatibles avec la superposition de couches actives multiples.

Conséquences : nœuds de fabrication plus complexes et coûteux, gains de performance plus courts, et une chaîne d’approvisionnement concentrée dans peu d’acteurs, produisant autant un enjeu physique que géopolitique.

La proposition de Pékin : un GAAFET 2D à base de bismuth… et son diélectrique « natif »

Le groupe mené par Hailin Peng (Université de Pékin) conçoit un GAAFET à deux dimensions dans lequel :

- Le canal est Bi₂O₂Se, un semi-conducteur 2D à haute mobilité électronique et à structure laminaire (couches liées par des forces de van der Waals), permettant interfaces propres et une épaisseur contrôlable à l’échelle atomique.

- La porte est isolée par Bi₂SeO₅, un dielélectrique pouvant croître à partir du canal (oxydation contrôlée), ce qui favorise une interface cristalline stable face aux dynamiques hétérogènes, illustrée par des expériences où l’on évite la formation d’états pièges (trap states).

Pourquoi cette combinaison est-elle stratégique ?

- Contrôle électrostatique « enveloppant ». En tant que GAA, la porte englobe le canal 2D, ce qui réduit la pente de seuil, augmente le on/off et limite la variabilité notamment pour les canaux courts. Les résultats du travail montrent un meilleur contrôle que pour un FET à porte unique classique.

- Interface « finement ajustée ». La paire Bi₂O₂Se / Bi₂SeO₅ présente une énergie de formation faible et une planéité atomique visible en STEM, rendant possible une basse dispersion et un faible hystérésis. Évitant les « colles » chimiques étrangères, on réduit la présence d’états pièges à la frontière canal-dielectrique.

- Diélectrique haute-κ. La constante diélectrique effective du Bi₂SeO₅ permet un Équivalent d’Épaisseur d’Oxyde (EOT) subnanométrique en empêchant la fuite d’électrons, contrairement au SiO₂ (~3,9), quand on veut réduire l’épaisseur sans compromettre la fiabilité. Traduction : on atteint plus de contrôle avec moins de voltage.

- Procédé à basse température. La déposition/Epitaxie à basse T évite de « cuire » le dessous, évènement pouvant compromettre la stabilité des structures 3D en silicium. Ici, on peut superposer directement des couches actives — 3D monolithique — sans détruire ce qui a été construit précédemment.

Une véritable intégration 3D monolithique : du plan à la « tour » de transistors

L’intégration 3D monolithique, distinguée de l’empilement classique, consiste à fabriquer des transistors fonctionnels et à les connecter verticalement dans des couches successives à l’intérieur de la même plaquette, sans recuire ni endommager la couche inférieure. Cela réduit la distance entre logique et mémoire, diminue les capacitances parasites de liaison, et ouvre la voie à une démesureur de la densité sans dépendre d’une nouvelle lithographie ultra-petite.

Sur le plan architectural, ce procédé rapproche la vision du CMOS 3D monolithique : NMOS et PMOS empilés (CFGET), macro blocs logiques avec SRAM très proche, buffers et cache directement au-dessus des unités de calcul. Avec comme avantage notable des tensions opérationnelles plus basses, qui atténuent la charge thermique : moins de watts par millimètre carré, donc un térmique global plus gérable.

Évaluation des performances : ce que révèle l’étude (et ce qu’elle ne dit pas)

Le rapport contient :

- Des GAAFETs 2D avec un canal d’environ 2,4 nm et un diélectrique d’environ 4,0 nm par côté ; des longueurs de porte pouvant descendre à ≈30 nm et des faisceaux opérationnels.

- Des pentes subthreshold proches du limite thermionique, avec des objectifs IRDS pour la prochaine décennie, ainsi qu’une hystérésis maîtrisée lors des cycles de balayage.

- Des résistances de contact mesurées via la méthode de longueur de transfert (TLM), avec une variabilité caractérisée dans les dispositifs à canal court.

- Une stabilité thermodynamique attestée par des études DFT et des preuves structurales, assurant une interface Bi₂O₂Se / Bi₂SeO₅ robuste face aux configurations classiques en Si/SiO₂ ou MoS₂/HfO₂.

Ce qui manque encore : une vraie microprocessseur ou une démonstration à l’échelle de la plaquette (12 pouces). Nous parlons de transistors et de matrices, avec des métriques intéressantes — on/off, SS, gm vs. Lch —, et d’un seuil thermique compatible avec la superposition. La transition du papier à la fabrication n’est pas encore accomplie, mais le couple matériau + procédé ouvre déjà deux grands axes pour le futur du silicium : interfaces et températures d’intégration.

Trois impacts majeurs si cette technologie se généralise

- Architecture des puces. Avec du monolithique 3D et des voltage plus faibles, il devient possible de co-localiser logique et mémoire, ce qui peut éliminer une partie du goulot d’étranglement mémoire-CPU/IA. Imaginez des matrices pour l’inférence ou des SRAMs à éloignement réduit ; moins de distance = moins d’énergie par opération.

- Centres de données. Chaque pour cent d’efficacité supplémentaire compte. Si les voltage d’opération sont plus faibles et la densité logique plus forte, sans accroître les pertes parasitiques, le PUE (indice d’efficacité énergétique des centres) et le TCO s’amélioreraient significativement, notamment en réduisant la chaleur à évacuer.

- Géopolitique du silicium. Une industrie des matériaux 2D, avec leur diéléctrique natif, pourrait ouvrir de nouvelles chaînes de valeur hors du monocorde silicium classique. Cela ne sonnerait pas la fin du silicium — pas du jour au lendemain — mais pourrait détacher certains pays du circuit traditionnel, leur permettant d’innover et de s’affranchir de restrictions à l’exportation.

Les limites à ne pas ignorer

- Défis de l’échelle industrielle. Passer des laboratoires aux productions en série nécessite de grandes plaquettes (8-12 pouces), une contrôle précis de la variabilité, et une performance par lot compétitive. Rien de trivial pour la 2D.

- Contacts et métallisation. La fabrication de contacts à canaux 2D basse résistance, sans pinnig, à l’échelle massive, demeure un défi, malgré des progrès comme les contacts van der Waals ou la métallisation sélective.

- Écosystème EDA et PDKs. La mise en place de cellules standards, SRAMs et flows 3D impose des modèles compacts et des PDKs robustes; il manque encore des produits exploitables par les concepteurs.

- Compatibilité thermique lors du superposition de plusieurs couches actives. Même si le procédé est à basse T, la dissipation thermique globale du composant reste un enjeu, et la gestion thermique verticale reste à maîtriser.

La mort de la Loi de Moore ?

Plutôt que de « mourir », la Loi de Moore se « transforme ». Le simple escalade géométrique fait place à de nouveaux axes : matériaux 2D, géométries GAA, intégration monolithique 3D, co-design logistique/mémoire, packaging hétérogène, et spécialisations selon les workloads (IA, accélérateurs, CFET, chiplets). Le travail de Pékin illustre une nouvelle étape : la future « loi » sera une fusion de densités verticales, de basses Tension et d’interfaces propres, plutôt qu’une simple course aux nanomètres comme unité marketing.

Ce qu’il faut surveiller à l’avenir

- Reproductibilité indépendante. Confirmations par plusieurs laboratoires de la performance du GAAFET Bi₂O₂Se / Bi₂SeO₅ dans des métriques semblables.

- Démonstrateurs 3D avancés. Inverses CMOS, cellules SRAM, blocs logiques empilés avec interconnexion verticale à faible résistance / capacité.

- Intégration avec le silicium. Approches hybrides par exemple : logique 2D sur back-end silicium, pour faciliter une adoption plus rapide.

- Feuilles de route. Programmes pour la fabrication de masse (volume), outils (dépôt, lithographie, métrologie) adaptés au paradigme 2D.

En résumé

La microélectronique ne manque pas d’idées : lorsque le silicium ne peut plus suivre, les matériaux 2D et l’intégration 3D monolithique proposent une voie alternative. Le duo Bi₂O₂Se / Bi₂SeO₅ montre que canal et diélectrique peuvent **coévoluer** pour offrir un contrôle électrostatique renforcé, réduire les voltages, et surtout permettre la superposition. La transition du concept au produit demande encore de la recherche et de l’industrie, mais la tendance est claire : la « Loi de Moore » du futur reposera davantage sur plus de dimensions plutôt que sur de plus petits nanomètres.

Questions fréquentes

Qu’est-ce qu’un GAAFET 2D et en quoi diffère-t-il d’un FinFET en silicium ?

Un GAAFET (Gate-All-Around) entoure le canal à tous ses côtés, offrant un meilleur contrôle électrostatique qu’un FinFET (où la porte couvre trois faces du canal). Si le canal est également 2D (épaisseur atomique, interfaces van der Waals), cela réduit trap et dispersion à l’interface, améliorant on/off, subthreshold slope (SS) et + stabilité, surtout pour les petits canaux.

Pourquoi utiliser Bi₂O₂Se comme semi-conducteur et Bi₂SeO₅ comme diélectrique ?

Parce qu’ils forment une interface stable et plane à l’échelle atomique : le dielélectrique peut être couvé directement depuis le canal (oxydation contrôlée), ce qui réduit les défauts. Par ailleurs, Bi₂SeO₅ à haute-κ permet un EOT très faible sans risque de fuites, tandis que Bi₂O₂Se garantit une mobilité élevée.

En quoi consiste l’intégration 3D monolithique face à l’empilement classique ?

Les procédés classiques (p. ex., chiplets, mémoire HBM) empilent des composants déjà fabriqués. En revanche, la 3D monolithique construit des couches actives l’une sur l’autre dans la même plaquette, avec de très proches connexions verticales. Cela permet de réduire la latence, la consommation d’énergie, et d’augmenter la densité sans dépendre d’une lithographie ultrafine supplémentaire.

Quand peut-on espérer des processeurs commerciaux intégrant ces matériaux 2D ?

À court terme, ce devraient être d’abord des démonstrateurs (inverseurs, SRAM, blocs logiques), plutôt que des CPU ou GPU complets. La réussite dépendra de la mise à l’échelle industrielle : fabrication de plaquettes de 8-12 pouces, contrôle de la variabilité, et adaptation des PDKs. D’ici quelques années, si les programmes de fabrication à l’échelle de la plaquette et la performance par lot progressent, on pourrait voir apparaître des composants 2D spécialisés cohabitant avec le silicium traditionnel.

Quels en seraient les bénéfices pour les centres de données et l’efficacité énergétique ?

Des voltage d’opération plus faibles et une superposition monolithique diminuent la consommation par opération et la distance à parcourir pour transférer les données. Pour des applications massives (IA, analytique), cela permettrait des économies systémiques et une empreinte thermique réduite, impactant positivement le PUE et le TCO.

Guide ultime de la mémoire RAM : qu’est-ce que c’est, types, DDR4 vs DDR5 et comment choisir correctement