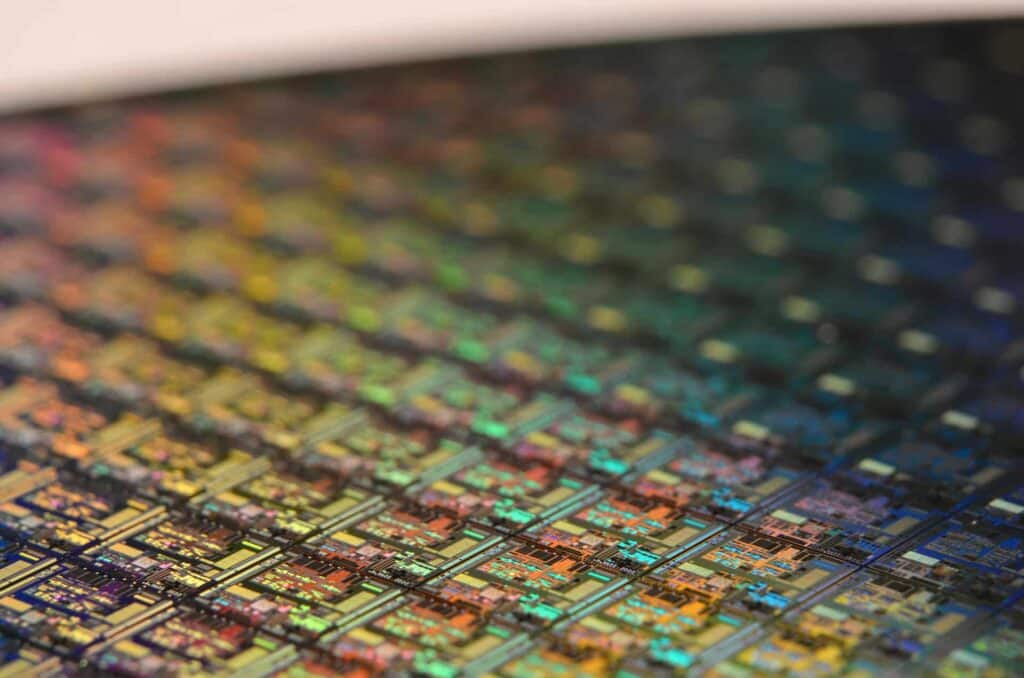

Le secteur des semi-conducteurs est habitué depuis des années aux gros titres sur la miniaturisation, mais le saut que propose aujourd’hui l’industrie sud-coréenne indique une frontière qui, jusqu’à récemment, relevait davantage du laboratoire que de la feuille de route. L’Institut Coréen des Ingénieurs en Semiconducteurs (The Korean Institute of Semiconductor Engineers) a publié son “Semiconductor Technology Roadmap 2026”, un document qui projette l’évolution technologique pour les quinze prochaines années et situe l’horizon de 2040 comme le début d’une nouvelle étape : l’arrivée de circuits logiques “de 0,2 nm” et l’introduction de structures telles que CFET et le monolithe en 3D.

Selon la diffusion d’ ETNews, cette prévision évoque une réduction drastique de la taille des circuits — jusqu’à une dixième de leur taille actuelle — ainsi qu’une transition de l’échelle du “nanomètre” vers celle de l’angstrom (Å), une unité utilisée lorsque l’on opère déjà à des décimètres de nanomètres.

De 2 nm actuels au grand saut de 2040

Cette feuille de route arrive à un moment où l’industrie commence à consolider la transition vers des architectures de transistors plus avancées. Par exemple, Samsung a présenté son Exynos 2600, un processeur mobile basé sur un procédé GAA (Gate-All-Around) de 2 nm, un jalon qui fixe la barre pour le “pionnier” d’ici 2025. À partir de là, le plan coréen envisage une amélioration continue qui culminerait en 2040 avec des nœuds logiques “de 0,2 nm”, soutenus par deux concepts clés :

- CFET (Complementary Field-Effect Transistor) : une évolution du transistor visant à empiler et combiner des dispositifs complémentaires pour continuer à augmenter la densité et la performance.

- Structuration 3D monolithique : une approche qui cherche à dépasser l’empilement traditionnel (packaging avancé) en construisant des couches fonctionnelles intégrées de manière beaucoup plus compacte.

En pratique, le message principal est clair : si la miniaturisation “plane” s’approche de ses limites, l’industrie doit adopter plus de verticalité et nouvelles architectures pour continuer à progresser.

Les détails du “0,2 nm” : plus qu’un chiffre, un symbole

Le chiffre “0,2 nm” est puissant, mais aussi délicat. Dans le monde réel, la désignation de nœud technologique ne correspond pas toujours à une mesure physique unique (comme la longueur de porte), et elle condense souvent plusieurs améliorations : densité, efficacité, performance, nouveaux matériaux et règles de conception. C’est pourquoi, lorsqu’un plan technologique évoque “0,2 nm”, il s’agit généralement d’une classe technologique ou d’un étape de miniaturisation, plutôt que d’une taille littérale de tous les éléments du transistor.

Pourtant, ce document fonctionne comme une déclaration d’intentions : la Corée du Sud souhaite officiellement affirmer que son industrie ambitionne de mener la prochaine phase d’innovation, même si le scaling pose chaque fois des défis plus complexes : variabilité, fuites, dissipation thermique, limites des interconnexions et une fabrication qui frôle les frontières où la physique devient le plus grand adversaire.

Neuf “technologies cœur” : du procédé au circuit d’Intelligence Artificielle et à la computation quantique

Le plan ne se limite pas à dire “nous irons vers des nœuds plus petits”. Selon ETNews, son objectif est de renforcer la compétitivité technologique et industrielle à long terme, de dynamiser la recherche académique et de guider les stratégies de formation des talents. Pour cela, il structure ses prévisions autour de neuf technologies considérées comme essentielles :

- Dispositifs et procédés de semi-conducteurs

- Semi-conducteurs pour l’Intelligence Artificielle

- Interconnexion optique

- Capteurs semi-conducteurs pour la connectivité sans fil

- Semi-conducteurs pour la connexion câblée

- PIM (Processing-In-Memory)

- Packaging

- Calcul quantique

- (Et l’ensemble des orientations technologiques regroupées comme axes d’évolution dans le document)

Ce catalogue reflète un changement de mentalité : l’avenir ne dépend pas uniquement du “nœud” mais du système complet. La vitesse n’est plus seulement une question de transistors plus petits, mais aussi d’interconnexion améliorée, de mémoires plus rapides, de packaging avancé et d’architectures conçues pour des charges spécifiques, en particulier dans l’Intelligence Artificielle.

Mémoire : DRAM plus fine, HBM avec davantage de couches et un bond en largeur de bande

Ce qui intrigue particulièrement sur la feuille de route dans le domaine de la mémoire, principal goulot d’étranglement à l’ère de l’Intelligence Artificielle, ce sont les prévisions suivantes :

- DRAM : réduction des circuits du 11 nm au 6 nm

- HBM (High-Bandwidth Memory) : saut de 12 couches et 2 To/s à 30 couches ou plus et 128 To/s

Il s’agit d’une projection ambitieuse mais cohérente avec la direction du secteur : les accélérateurs d’Intelligence Artificielle et les systèmes à hautes performances sont de plus en plus dépendants de la rapidité avec laquelle ils peuvent déplacer les données, pas uniquement de leur puissance brute de calcul. Par conséquent, l’évolution de la HBM —plus de couches et un débit supérieur— devient une course stratégique cruciale.

NAND : de 321 à 2 000 couches

Le plan chiffre également un objectif qui, par sa grandeur, semble délibérément provocateur : la mémoire NAND flash pourrait passer de ses 321 couches actuelles à un sommet prévu de 2 000 couches.

Ce message est double. D’une part, l’industrie maintient sa volonté de croissance par empilement vertical. D’autre part, elle indique que la complexité (fabrication, performance, coûts) va inévitablement augmenter, et que le stockage restera une composante centrale aussi bien pour les centres de données que pour tout l’écosystème des dispositifs.

Chips d’Intelligence Artificielle : du présent à la “top league” des “TOPS”

Dans le domaine des semi-conducteurs pour l’Intelligence Artificielle, ETNews relaye une autre prévision qui résume la logique du plan : en 15 ans, une progression significative en termes de performance opérant en opérations par seconde est attendue.

Le document compare la situation de départ — avec une référence de 10 TOPS par watt — à un horizon où les puces pourraient atteindre 1 000 TOPS pour l’apprentissage et 100 TOPS pour l’inférence.

Au-delà des chiffres, la leçon est claire : la croissance de l’Intelligence Artificielle ne sera pas soutenable sans améliorations radicales en efficacité et architectures, et l’industrie sud-coréenne veut jouer un rôle central dans cette révolution.

Un plan technologique également un levier politique

Ces documents ne sont pas uniquement des prédictions : ils servent de outils de coordination entre industrie, universités et administrations. ETNews souligne que l’Institut prévoit de mettre à jour et réviser régulièrement le plan, en élargissant ses objectifs selon les avancées technologiques.

Dans un contexte mondial de compétition entre blocs — États-Unis, Chine, Corée du Sud, Taïwan et Europe —, une feuille de route de ce genre agit à la fois comme un message interne (priorités d’investissement, formation de talents) et comme une déclaration d’intention envers l’extérieur (soutenir le leadership). Et surtout, elle confirme une réalité : l’avenir du chip ne se limite pas à une seule métrique. Il résultera d’une combinaison de nouvelles architectures de transistors, intégration 3D, mémoire avancée, interconnexion et packaging.

Questions fréquentes

Que signifie entrer dans “l’ère de l’ångström” en semi-conducteurs ?

Cela implique de travailler à des échelles de décimètres de nanomètre et de repousser des limites physiques de plus en plus exigeantes. En pratique, cela désigne souvent une nouvelle étape de miniaturisation et d’architecture, et non simplement un changement d’unité.

Un nœud “0,2 nm” est-il littéral ou s’agit-il d’une expression pour désigner une classe technologique ?

Généralement, cela réfère à une “classe” de nœud ou à un ensemble d’innovations technologiques. Les noms de nœuds ne correspondent pas toujours à une dimension physique précise à l’intérieur du transistor.

Qu’est-ce que le CFET et pourquoi est-il clé pour 2040 ?

Le CFET est une architecture de transistor complémentaire visant à continuer à augmenter la densité et l’efficacité lorsque le scaling traditionnel devient insuffisant. Il est souvent associé à des stratégies d’intégration plus verticale.

Pourquoi l’HBM et le débit en bande passante sont-ils si importants à l’ère de l’Intelligence Artificielle ?

Parce que de nombreux systèmes d’IA sont limités par le déplacement des données. Augmenter le nombre de couches et la largeur de bande dans la HBM aide à alimenter le calcul avec plus de données et à réduire les goulets d’étranglement.

via : etnews