Intel Révolutionne le Marché avec Lunar Lake

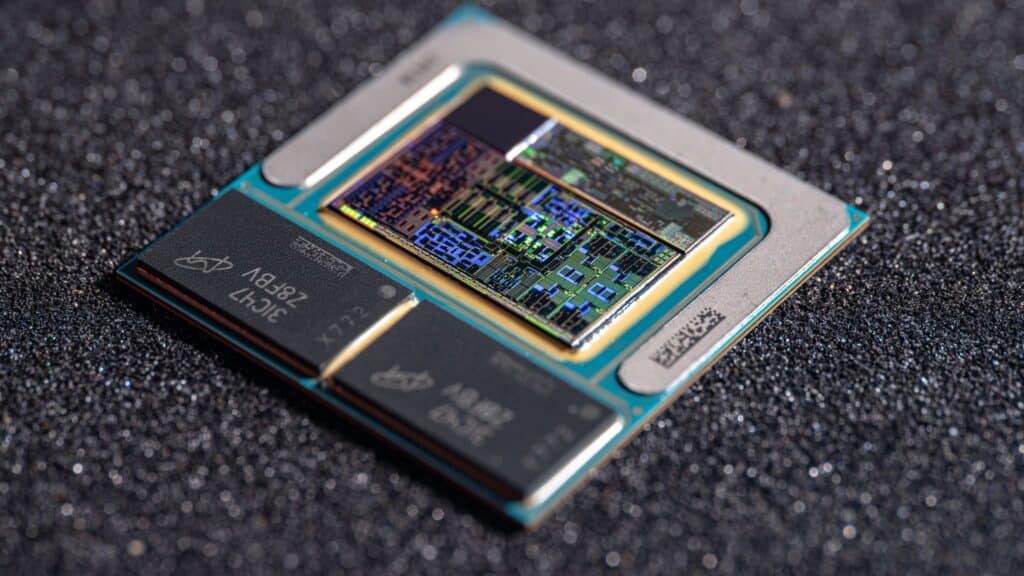

Intel a récemment marqué le marché avec le lancement de Lunar Lake, un processeur innovant qui allie l’efficacité des systèmes sur puce (SoC) ARM à la puissance traditionnelle du x86. De nouvelles images haute résolution du cœur de la puce, publiées par le célèbre photographe Fritzchen Fritz, révèlent comment Intel parvient à réaliser cet équilibre, une architecture que même l’ancien PDG Pat Gelsinger qualifie d’unique.

Une Approche Hybride Sans Précédent

Bien que Lunar Lake et Arrow Lake partagent certaines technologies clés, telles que les microarchitectures et le process de fabrication, Intel a opté pour des chemins de design totalement distincts. Lunar Lake repose sur un Compute Tile fabriqué par TSMC en process N3B, intégrant quatre cœurs P (Lion Cove) avec 12 Mo de cache L3 partagé et 2,5 Mo de L2 par cœur. La gestion de l’efficacité énergétique est confiée à un cluster de cœurs E (Skymont), situé sur une « île à basse consommation » avec son propre cache L2 de 4 Mo, isolé du cœur principal.

Une Puce Pour l’Ère de l’IA

À côté du cluster de cœurs E, se trouve une Unité de Traitement Neuronal (NPU) capable d’accueillir jusqu’à six moteurs NCE, avec une puissance estimée à 48 TOPS (billions d’opérations par seconde). Lunar Lake devient ainsi un acteur de premier plan dans le domaine de l’informatique accélérée par IA, surpassant largement les générations précédentes de processeurs mobiles.

GPU Intégré Battlemage et Cache Partagé

Le Compute Tile intègre également une GPU basée sur l’architecture Battlemage, dotée de jusqu’à huit cœurs Xe2-LPG, ainsi qu’un moteur multimédia performant. Tous ces éléments sont unifiés sous un cache SLC (System-Level Cache) de 8 Mo, partagé entre les unités CPU, GPU, NPU, et les moteurs de médias. Pour diminuer les latences, Intel a positionné la couche mémoire physique directement au-dessus du Compute Tile, sous les modules LPDDR5x-8533 soudés, disponibles en versions de 16 Go ou 32 Go, rendant la mémoire non extensible.

Contrôleurs et Connectivité dans un Design Modulaire

Sous le Compute Tile se trouve le Platform Controller Tile, réalisé en process TSMC N6. Cette section contient les interfaces principales d’entrée/sortie : USB, Thunderbolt, PCIe 4.0/5.0, ainsi que Wi-Fi et Bluetooth. Ce chiplet agit comme un extend I/O, similaire au SoC Tile d’Arrow Lake, monté sur un interposeur actif basé sur le process 22FFL. Tous les chiplets sont interconnectés grâce à la technologie avancée d’empaquetage 3D Intel Foveros.

Révolution ou Expérience Unique ?

Bien que Lunar Lake ait été conçu comme un saut stratégique, Intel a laissé entendre qu’aucun successeur direct n’était prévu dans ses feuilles de route filtrées. Cela renforce l’idée qu’il s’agit d’une architecture de transition ou d’une expérience technologique. Néanmoins, la puce offre une efficacité impressionnante, des performances graphiques prometteuses et une intégration poussée, se rapprochant du modèle de conception des puces Apple Silicon ou des Snapdragon X Elite.

Lunar Lake n’arrivera sur les ordinateurs portables commerciaux qu’en 2025, mais a déjà suscité un grand intérêt dans l’industrie. Avec une architecture mélangeant les meilleures caractéristiques des mondes ARM et x86, son impact pourrait dépasser celui d’une simple expérimentation.

Image mise en avant : © Fritzchen Fritz – Vue en haute résolution du die de Lunar Lake.

Source : Tom’s Hardware