La compétition pour l’Intelligence Artificielle ne se décide pas uniquement avec des GPU. Le nouveau goulet d’étranglement — silencieux, coûteux et de plus en plus déterminant — réside dans la mémoire : sa capacité à déplacer des données en une seconde, sa proximité avec le processeur, et l’énergie nécessaire pour maintenir ce flux constant. En plein 2026, avec l’expansion des centres de données à un rythme qui met à rude épreuve le réseau électrique et les chaînes d’approvisionnement, l’attention se tourne vers un composant longtemps considéré comme « standard » : la DRAM.

Le constat est clair. Des entreprises comme TrendForce ont fortement revu à la hausse leurs prévisions d’augmentations de prix pour la mémoire conventionnelle, dans un marché tendu par la demande accrue d’infrastructure pour l’IA et par la préférence des grands fabricants pour des capacités plus rentables telles que la HBM (High Bandwidth Memory). Parallèlement, cet impact commence à se faire sentir dans l’électronique grand public : plusieurs fabricants de PC envisagent désormais de se fournir en Chine en raison de la pénurie mondiale.

Dans ce contexte, un mouvement notable se profile : SoftBank, via sa filiale SAIMEMORY, a signé un partenariat avec Intel pour faire progresser la commercialisation d’une technologie nommée Z-Angle Memory (ZAM). Il s’agit d’une mémoire de nouvelle génération conçue pour combiner grande capacité, bande passante élevée et faible consommation, avec pour objectif des charges de travail relatives à la formation et à l’inférence de modèles à grande échelle.

Un calendrier précis : prototypes en 2027 et mise sur le marché en 2029

Ce partenariat a été scellé le 2 février 2026. Selon le plan officiel, des prototypes verront le jour durant l’année fiscale se terminant le 31 mars 2028 (FY2027), avec pour ambition leur commercialisation dès FY2029. SAIMEMORY, créée en décembre 2024, prendra en charge le développement et la mise sur le marché, tandis qu’Intel fournira la base technologique et le support en innovation.

SoftBank inscrit cette démarche dans sa stratégie de renforcement des infrastructures liées aux centres de données et à l’IA, soulignant une étape clé : passer de l’entraînement massif à l’inférence opérationnelle, où le déplacement de gros volumes de données vers les accélérateurs devient crucial.

Qu’est-ce que ZAM et pourquoi l’“axe Z” est-il essentiel ?

ZAM est une architecture mémoire qui se projette vers le haut : comme son nom l’indique, elle exploite l’axe Z, c’est-à-dire le empilement vertical de couches pour augmenter capacité et performance sans gonfler la taille physique. Le but, en termes simples, est de rapprocher une mémoire « rapide » des puces de calcul, en réduisant les frictions habituelles : latence, consommation d’énergie et contraintes d’intégration.

Bien que le projet en soit encore à ses débuts, plusieurs analyses sectorielles le voient comme une tentative de surpasser les limitations actuelles de la HBM, qui a été clé pour l’IA grâce à son énorme bande passante, mais qui impose aussi des compromis en termes de capacité et de coûts. En somme, le secteur pourrait avoir besoin de mémoires qui permettent de concilier, sans compromis, « plus de bande passante » et « plus de capacité ».

La avancée technique d’Intel : la bonding de DRAM de nouvelle génération (NGDB)

Le cœur technologique de cet accord repose sur le projet Next Generation DRAM Bonding (NGDB) d’Intel, développé dans le cadre du programme Advanced Memory Technology (AMT), soutenu par le Département de l’Énergie des États-Unis et la National Nuclear Security Administration, avec l’appui de laboratoires nationaux tels que Sandia.

Sandia a publié de manière publique certains avancements importants : ils indiquent qu’en mémoire à haute bande passante, on améliore souvent le débit au détriment d’autres facteurs, comme la capacité. NGDB cherche à réduire ces compromis en « rapprochant » performances de la HBM et de la DRAM classique, tout en améliorant l’efficacité énergétique. L’un de leurs prototypes montre des assemblages avec une couche de base et huit couches de DRAM empilées verticalement. Les prototypes les plus récents montrent déjà une DRAM opérationnelle via cette technique d’empilement.

Sandia résume son ambition en ces termes : concevoir une mémoire haute performance « prête pour la fabrication à grande échelle ».

Financement, industrie et enjeu stratégique pour l’approvisionnement

Bien que le communiqué officiel se concentre sur la feuille de route, des médias spécialisés indiquent que SoftBank prévoit d’investir environ 3 milliards de yens pour atteindre le stade des prototypes en 2027, une information provenant de sources du secteur citées dans la couverture spécialisée.

Ce mouvement s’inscrit aussi dans une logique stratégique : le Japon, autrefois acteur majeur dans la mémoire, cherche aujourd’hui à renforcer sa position dans les secteurs clés de la chaîne de valeur de l’IA. Si ZAM mature, il ne sera pas seulement un composant : ce serait une véritable levière pour réduire la dépendance technologique dans un marché où la demande devient à la fois politique, industrielle et géopolitique.

Le contexte mondial demeure tendu : la pénurie de mémoire et la réaffectation des capacités vers l’IA bouleversent prix, calendrier de lancement et stratégies d’approvisionnement, depuis les centres de données jusqu’aux ordinateurs portables grand public.

Ce qui reste à démontrer

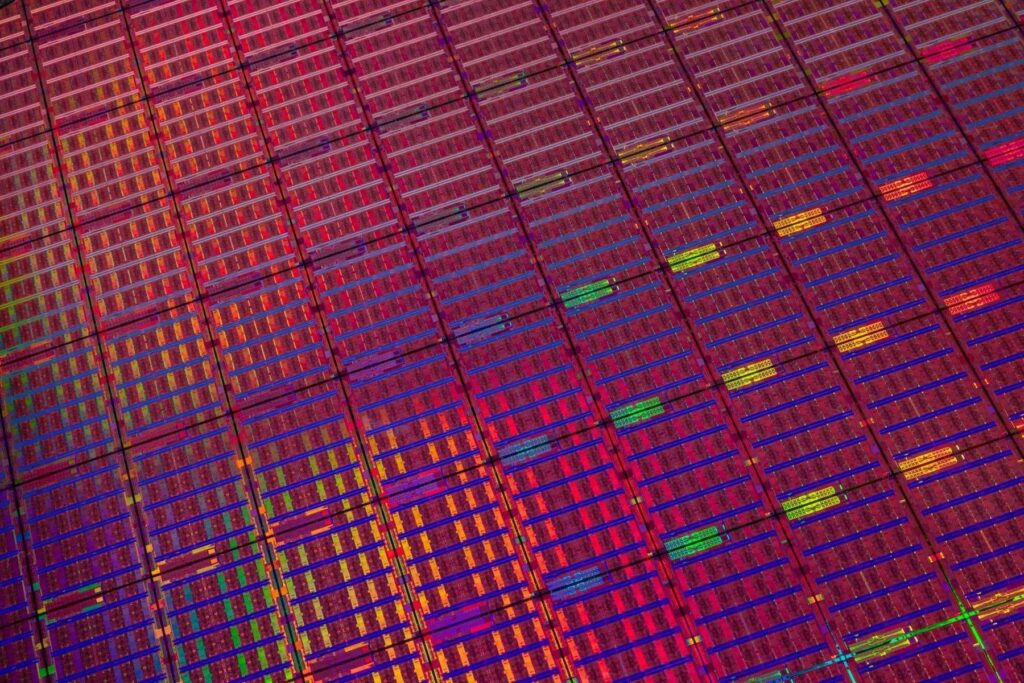

Pour l’instant, ZAM n’est qu’une promesse avec un calendrier, pas un produit prêt à la commercialisation. Entre l’annonce et la fabrication à grande échelle, de nombreux obstacles connus dans le secteur des semi-conducteurs subsistent : rendement par wafer, dissipation thermique dans des empilements denses, complexité de l’intégration, standardisation pour une adoption en serveurs, et surtout, coût final en regard des options déjà éprouvées.

Cependant, le message du marché demeure clair : si l’IA est une course infrastructurelle, la mémoire en est aujourd’hui la zone de potentiel le plus important pour faire des avancées ou des revers. Et lorsque le secteur trébuche, naissent des opportunités pour de nouvelles architectures, des alliances improbables et des retours stratégiques inattendus.

Questions fréquentes

En quoi la mémoire HBM diffère-t-elle de la mémoire DDR4/DDR5 classique dans les serveurs d’IA ?

La HBM privilégie un débit extrêmement élevé grâce à un empaquetage avancé et une proximité immédiate avec le processeur, ce qui est crucial pour alimenter GPU/accélérateurs ; la DDR est utilisée comme mémoire principale plus générale, offrant plus de flexibilité et un coût moindre par capacité, mais avec un débit par rapport inférieur.

Quand peut-on espérer voir les premiers systèmes commerciaux avec Z-Angle Memory (ZAM) ?

Le plan prévoit des prototypes en 2027 et une commercialisation en 2029. Leur arrivée en produits finis dépendra cependant de l’industrialisation et des accords avec les fabricants de plateformes.

Pour quelles raisons la mémoire est-elle devenue un goulet d’étranglement pour l’Intelligence Artificielle ?

Les grands modèles et l’inférence à grande échelle nécessitent de déplacer en permanence des données vers les accélérateurs. Lorsqu’il manque de bande passante ou de capacité proche du calcul, la GPU peut rester « en attente », ce qui augmente le coût de chaque entraînement et de chaque service.

Comment la pénurie de DRAM et NAND impacte-t-elle utilisateurs de PC et entreprises ?

Lorsque les prix augmentent ou les approvisionnements se font rares, les fabricants ajustent leurs configurations, retardent leurs lancements, ou cherchent des fournisseurs alternatifs. Pour les entreprises, cela peut se traduire par des coûts supplémentaires pour les serveurs, des extensions ou des renouvellements d’équipements.

source : trendforce

RCS Universal Profile 4.0 est désormais officiel : comment se compare au SMS, aux versions précédentes de RCS et à WhatsApp