La lithographie EUV de haute ouverture numérique (High-NA) se présente depuis plusieurs années comme la clé pour continuer à réduire la taille des composants lorsque le scaling traditionnel commence à se heurter aux limites de la physique. Cependant, dans les cercles techniques et lors de discussions avec des experts, se fait progressivement jour une vision moins héroïque et plus pragmatique : acheter une machine ne garantit pas une production en volume. La réalité, souvent rappelée lors de conversations récentes dans l’industrie, est que le véritable indicateur de maturité de la technology High-NA ne réside pas seulement dans le matériel fourni par ASML, mais surtout dans la maturité de l’écosystème qui l’entoure. Et dans cet écosystème, une composante arrive toujours en premier : la OPC (Optical Proximity Correction).

La polémique renaît autour d’une question précise : Intel rencontre-t-elle des obstacles avec la High-NA EUV pour son noeud 14A, en raison de problèmes liés à l’OPC et à la préparation du flux de fabrication ? La réponse est importante, car Intel a placé la High-NA au cœur de sa stratégie pour regagner du terrain dans la course aux noeuds avancés. De l’autre côté du Détroit, TSMC adopte une position différente : TSMC continue d’évaluer la High-NA, mais ne semble pas prête à l’adopter à court terme, même dans des générations où, sur le papier, ses avantages en termes de complexité de masque pourraient apparaître.

Pourquoi la High-NA n’est pas “plug and play”

La High-NA EUV (NA 0,55) promet une résolution accrue par rapport à la EUV « conventionnelle » (Low-NA), avec la possibilité de réduire le multipatronage et de simplifier certains processus. C’est la théorie. En pratique, selon le secteur, l’introduction d’une machine de cette envergure nécessite bien plus qu’un simple recalibrage du scanner : matériaux, masques, métrologie, contrôle du processus, variabilité, overlay et surtout puissance de calcul.

Dans cette chaîne, la OPC apparaît comme le « premier verrou » à franchir. La correction optique de proximité consiste, en termes simples, à ajuster le pattern du masque pour que l’image imprimée sur la plaquette corresponde à la conception première, en compensant les distorsions optiques et de procédé. Plus le nœud est avancé, plus la OPC doit être fine et robuste. Et lorsque l’on passe à une ouverture NA plus grande — comme avec la High-NA — le travail d’ajustement des modèles, de calibration et de validation devient encore plus critique.

C’est dans ce contexte qu’a été entendue l’avertissement lors d’un appel avec des experts récemment relayé dans l’industrie : même si Intel dispose d’outils High-NA, la OPC « n’est pas encore prête » pour supporter une production en volume immédiate. La raison est que l’écosystème tout entier est encore en construction. Par ailleurs, un facteur temporel est critique : un noeud avancé ne se décide pas du jour au lendemain, et beaucoup d’aspects — matériaux, flux, calibration — doivent être anticipés plusieurs années à l’avance. Si le fluide de fabrication n’est pas prêt à temps, il devient difficile de l’introduire sans retarder toute la feuille de route.

TSMC, une approche pragmatique et planifiée

Pour sa part, TSMC adopte une posture prudente. La société a publiquement indiqué qu’elle continue d’évaluer la High-NA, mais qu’elle ne voit pas encore de nécessité immédiate pour certaines générations, surtout en raison du coût et du rapport bénéfice/risk. La décision ne se limite pas à la partie technologique : elle se base aussi sur le throughput réel, la stabilité, le coût par plaquette et la comparaison avec des solutions basées sur le Low-NA, souvent multipatronnées, et intégrant une optimisation du processus.

Déjà en mai 2025, Reuters rapportait que TSMC poursuivait son évaluation de la High-NA, en exprimant des réticences dues au prix et au manque d’un avantage suffisamment convaincant à cette étape de leur stratégie. La tendance pour 2026 est claire : si TSMC ne perçoit pas une nette amélioration en termes de coût ou de risque, elle repoussera l’adoption, même si Intel cherche à faire de la High-NA un argument différenciateur commercial.

Dans le même temps, il a été indiqué que TSMC ne prévoit pas d’utiliser la High-NA pour son noeud A14, ce qui confirme une stratégie prudente : maximiser l’exploitation du Low-NA, limiter l’augmentation des coûts liés aux masques, et éviter un surcoût prématuré.

Intel 14A : une dépense visible, des incertitudes invisibles

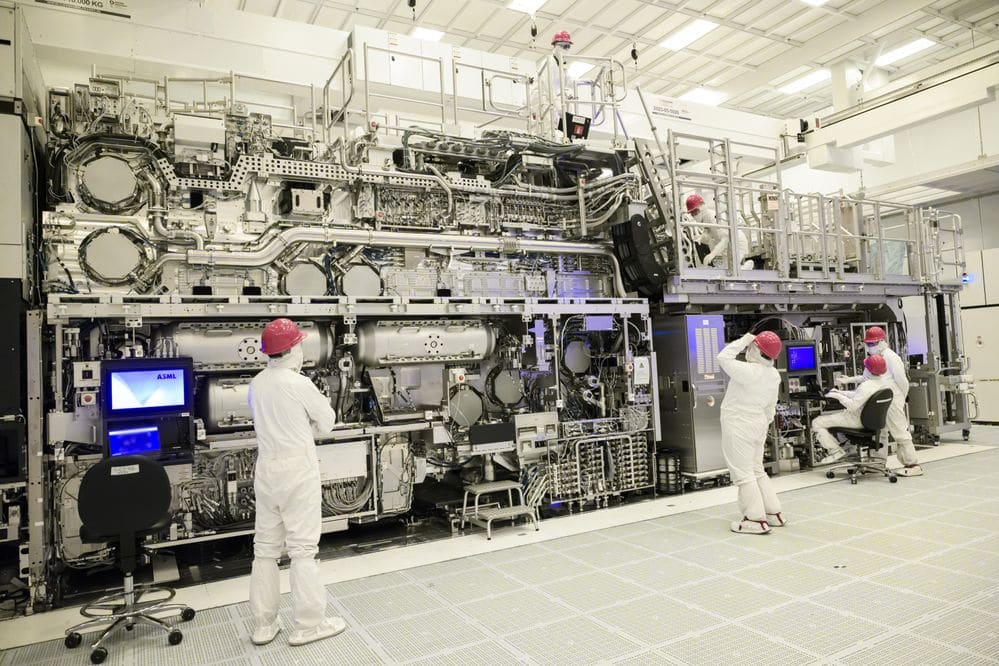

Pour Intel, la mise en place de la High-NA est devenue un symbole d’ambition industrielle. Récemment, l’installation d’un outil de production High-NA (EXE:5200B) a été annoncée comme une étape importante dans la feuille de route vers le noeud 14A, car elle dépasse le cadre de la recherche et exploration pour s’approcher des conditions réelles de production, où la fiabilité, la reproductibilité et le rendement jouent un rôle clé.

Le problème, c’est que même avec cette machine installée, la réussite dépend de l’intégration globale : si le flux OPC, la validation et le contrôle de processus n’atteignent pas le niveau requis pour une fabrication à haut volume, la High-NA pourrait se limiter à une « avance partielle » (par exemple, pour certains types de couches ou phases), ou rester une option à moyen / long terme plutôt qu’un levier immédiat de leadership. En 2025, des signaux indiquaient aussi qu’Intel envisagerait des alternatives pour ne pas dépendre exclusivement de la maturité de la High-NA, par souci de gestion des risques calendaires.

Ce positionnement illustre le constat qu’Intel dispose d’un « peu plus de marge » en restant en retrait par rapport à TSMC pour certaines étapes, mais qu’il ne peut pas attendre indéfiniment que tout l’écosystème High-NA, notamment l’OPC, atteigne une maturité industrielle complète.

Ce qui est réellement en jeu : crédibilité, coûts et clients

Au-delà du débat purement technique, il s’agit aussi d’une question de stratégies commerciales. La High-NA nécessite des équipements extrêmement coûteux, et un investissement en capital qui n’est justifié que si le volume de production est suffisant, surtout pour la foundry de services. Toute incertitude sur la maturité de l’ensemble du flux — OPC incluse — peut être perçue comme un signal de risque par les clients, qui planifient leurs designs plusieurs années à l’avance.

Ironie de la situation, la High-NA a été longtemps présentée comme « la grande solution » pour éviter la complexité du multipatronage, mais aujourd’hui, la discussion tourne autour d’aspects moins « glamour » : logiciel, modèles, calibration, puissance de calcul pour l’OPC. En résumé, la machine elle-même pourrait ne pas être la seule limite ; ce sont aussi toutes les pièces invisibles du processus, indispensables pour garantir une fabrication fiable à grande échelle.

À court terme, l’industrie semble suivre deux stratégies : d’un côté, Intel cherche à faire de la High-NA un différenciateur à travers le noeud 14A, et de l’autre, TSMC maintient une posture prudente, retardant son adoption jusqu’à ce que les coûts ou le risque soient plus favorables, ou qu’une génération spécifique ne le nécessite réellement. Entre ces approches, une constante demeure : en matière de semiconducteurs, l’innovation ne s’installe pas, elle se construit industriellement.

Questions fréquentes (FAQ)

Qu’est-ce que l’OPC en lithographie et pourquoi pourrait-elle freiner l’adoption de la High-NA EUV ?

L’OPC (Optical Proximity Correction) ajuste les motifs du masque pour que l’image imprimée en usine corresponde à la conception initiale, malgré les distorsions optiques ou de procédé. Avec la High-NA, les conditions optiques évoluent, rendant les modèles et calibrations plus complexes ; si le flux OPC n’évolue pas, la production en volume risque d’être compromise.

Pourquoi TSMC pourrait hésiter à utiliser la High-NA EUV pour l’A14, voire à considérer l’A10 ?

La décision se fonde principalement sur le calendrier et le coût par wafer : si le Low-NA EUV optimisé avec multipatronage offre un bon compromis, TSMC peut repousser la High-NA jusqu’à ce qu’elle devienne indispensable ou rentable.

Qu’implique le fait qu’Intel ait installé une EXE:5200B de High-NA EUV ?

C’est un jalon industriel : la machine est conçue pour la production, pas uniquement pour la R&D. Cependant, son installation ne garantit pas une utilisation immédiate à haute cadence ; cela dépend de l’intégration globale de l’écosystème (matériaux, métrologie, OPC, contrôle).

La High-NA EUV réduit-elle toujours le nombre de masques ou le coût de fabrication ?

Pas forcément. Elle peut simplifier certaines couches, mais le coût des équipements, la complexité des flux, et la maturité de l’écosystème peuvent contrebalancer ces avantages, surtout dans les phases initiales.

Litho bros, quick question — can you help me with one thing?

On an expert call, they said Intel’s adoption of High-NA EUV doesn’t really mean much. And they mentioned TSMC is barely even considering High-NA EUV, even for A10.

I’ll paste an excerpt below:

Q. Previously, Intel…

— Jukan (@jukan05) 18 janvier 2026