La course à la réduction de la taille des transistors — et, par conséquent, à l’amélioration des performances et de l’efficacité des puces destinées aux centres de données, à l’informatique haute performance et aux charges de travail en intelligence artificielle — se joue désormais sur deux fronts simultanément : laminage plus précis et nouvelles architectures/matériaux permettant de poursuivre la miniaturisation lorsque le silicium frise ses limites physiques.

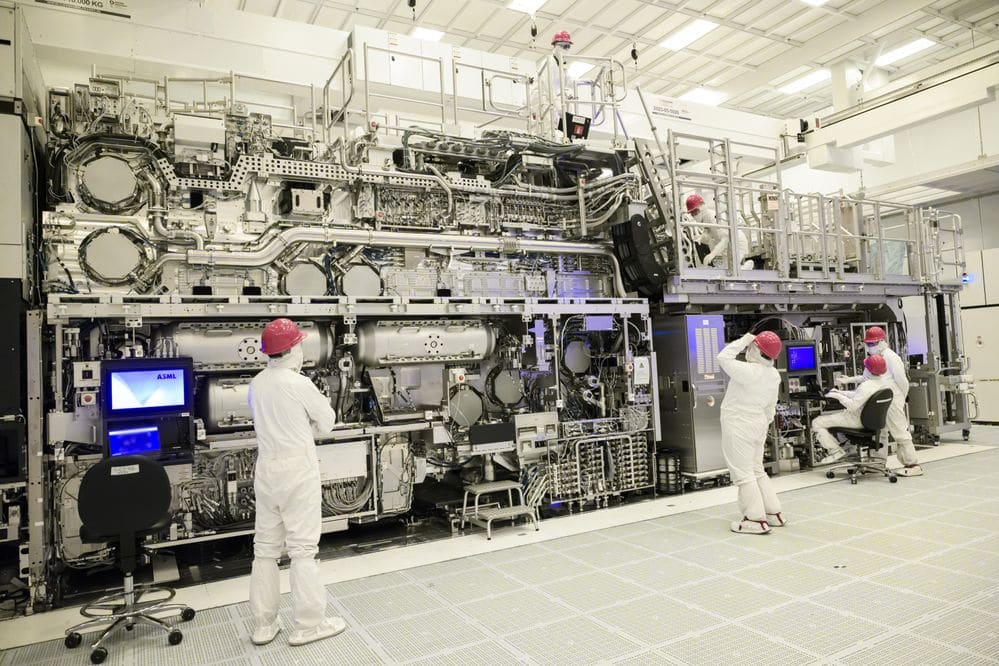

Dans cette double approche s’inscrit la dernière étape franchie par Intel Foundry, qui a annoncé des avancées dans deux projets distincts mais liés par un même objectif : convertir l’innovation en laboratoire en processus manufacturables. D’un côté, l’entreprise a atteint, en collaboration avec ASML, la phase de acceptance testing du TWINSCAN EXE:5200B, l’un des équipements les plus avancés de lithographie EUV à haute ouverture numérique (High NA EUV). De l’autre, Intel et Imec ont présenté des résultats d’intégration sur des plaquettes 300 mm pour des transistors à base de matériaux 2D, un axe de recherche visant à dépasser la miniaturisation que le silicium pourrait soutenir à l’avenir.

High NA EUV : du “cela fonctionne” au “cela produit”

En lithographie, il ne suffit pas de démontrer qu’un nouvel outil peut imprimer des motifs plus fins. La véritable barrière réside dans la capacité à transformer cette aptitude en productivité, répétabilité et contrôle, à des rythmes compatibles avec une fabrication moderne. L’annonce d’Intel situe le EXE:5200B précisément dans cette étape : le passage de la validation technique à des indicateurs pertinents pour la production.

D’après les données partagées, le EXE:5200B conserve la haute résolution de la première génération (EXE:5000), tout en relevant deux indicateurs particulièrement sensibles :

- Jusqu’à 175 wafers par heure de sortie, une mesure de productivité adaptée aux environnements de fabrication avancés.

- Overlay de 0,7 nanomètres, c’est-à-dire une amélioration de la précision d’alignement entre couches lithographiques, critique lorsque chaque nanomètre compte et que tout décalage se traduit par des pertes de performance ou de rendement.

La collaboration avec ASML s’appuie également sur une expérience antérieure : Intel rappelle que son utilisation du High NA EUV a débuté en 2023 avec l’arrivée du premier système commercial High NA dans son centre d’innovation en Oregon. Depuis, l’objectif a été de valider non seulement la résolution, mais aussi tout l’écosystème nécessaire pour rendre la lithographie utile à grande échelle : masques, gravure, métrologie et techniques d’amélioration de la résolution.

Les changements apportés par le EXE:5200B

Sur le plan technique, Intel décrit trois axes d’innovation clés qui expliquent la pertinence de cette génération :

- Source EUV à plus haute puissance

Une puissance accrue permet une exposition plus rapide à des doses pratiques, offrant une meilleure fenêtre de processus pour des motifs à contraste élevé et, élément crucial, réduit les défauts tels que la rugosité des bords ou l’écartement de ligne, qui deviennent plus perceptibles à mesure que les motifs se rétrécissent. - Nouvelle architecture de “wafer stocker”

À première vue, cela évoque la logistique, mais en fabrication avancée, la logistique est physique : stabilité thermique, manipulation cohérente des lots et réduction de la dérive opérationnelle. Ceci est particulièrement vital dans les flux nécessitant plusieurs passes ou expositions, où toute variation peut se multiplier. - Contrôle d’alignement plus précis

L’overlay de 0,7 nm s’explique par des avancées dans la gestion du stage, la calibration des capteurs et l’isolation environnementale. En clair : un contrôle accru sur le comportement du système en conditions réelles, indispensable pour intégrer le High NA EUV dans des couches critiques.

Ce que cela signifie pour les concepteurs, ce n’est pas seulement “plus de science”, mais des règles de conception plus flexibles, la possibilité de réduire le nombre d’étapes et de masques, pour un processus plus simple susceptible d’aboutir à de meilleurs rendements et à une montée en cadence vers une production stable. Intel insiste toutefois sur le fait que l’industrie en est encore à ses débuts dans cette voie.

Au-delà du silicium : transistors 2D sur des plaquettes de 300 mm

Le deuxième front, plus orienté à long terme, n’en est pas moins stratégique. Intel avancé une idée de plus en plus répandue dans la recherche : un moment viendra où les dimensions seront si petites que les atomes de silicium cesseront de se comporter de manière “idéale” pour continuer à améliorer les performances.

Les matériaux 2D peuvent alors jouer un rôle clé en étant organisés en couches de seulement quelques atomes d’épaisseur. Intel cite la famille des dicalcogénures de métaux de transition (TMD) comme candidates prometteuses, grâce à leur contrôle de la conduction et leur potentiel d’évolutivité. Le défi, en toute transparence, est que faire progresser ces matériaux en laboratoire ne garantit pas leur fabrication à grande échelle en plaquettes de 300 mm.

Dans ce contexte, Intel et Imec ont présenté lors de l’IEDM une avancée qu’ils considèrent comme fondamentale : une intégration manufacturable en 300 mm de contacts source/drain et módules de la pile de portes pour transistors 2D (2DFETs), utilisant :

- WS₂ et MoS₂ pour les transistors n-type

- WSe₂ pour les transistors p-type

Le point central de cette approche est un gravure sélective d’oxyde appliquée sur des couches 2D de haute qualité, croissance réalisée par Intel, responsables d’un empilement AlOx/HfO₂/SiO₂. Cette technique permet de créer des contacts supérieurs de type damascène, intégrant le métal dans une structure en “tranchée”, sans compromettre l’intégrité du canal 2D sous-jacent.

L’enseignement implicite est clair : le principal obstacle à la fabrication de transistors 2D n’est pas la compatibilité du matériau, mais la faisabilité de leur production à une échelle industrielle avec des modules de contact et une porte intégrés, compatibles avec un flux de fabrication standard.

“Manufacturabilité” : le maître-mot

Intel synthétise cette démarche par une conviction : l’innovation utile est celle qui s’intègre avec discipline. Elle transforme la nouveauté en fiabilité, en réduisant les risques lors de la transition du laboratoire à la production. Dans cette optique, la collaboration “ouverte” avec des acteurs comme ASML et Imec apparaît comme un accélérateur : elle permet d’accélérer les courbes d’apprentissage, de partager des composants, la métrologie, les modes de défaillance, et d’aider clients et écosystèmes à évoluer avec des contraintes de conception plus réalistes.

Le message clé pour le secteur est que l’ascension vers les prochaines générations de puces — notamment pour l’intelligence artificielle et les systèmes haute performance — ne repose pas uniquement sur un progrès exceptionnel, mais sur une synergie : des outils plus performants (High NA EUV) et de nouveaux matériaux/architectures (2D), dont la véritable réussite réside dans leur fabrication à grande échelle.

Questions fréquentes

Qu’est-ce que le High NA EUV et pourquoi est-il crucial pour les futures générations de puces ?

Il s’agit d’une version améliorée de la lithographie EUV, visant à imprimer des motifs plus fins avec une précision accrue. À des nœuds technologiques avancés, cette avancée peut simplifier le processus (moins d’étapes et de masques) tout en augmentant le rendement et la performance.

Que signifie “overlay de 0,7 nm” sur un scanner lithographique ?

C’est une mesure de l’alignement entre différentes couches. Plus cette valeur est faible, plus la superposition des motifs est précise, ce qui est essentiel pour éviter des défauts et maintenir un rendement optimal dans les technologies avancées.

Pourquoi évoque-t-on l’intérêt pour les matériaux 2D comme alternative future au silicium ?

Parce qu’au niveau très réduit, le silicium pourrait commencer à perdre de sa capacité à améliorer la performance. Les matériaux 2D offrent des canaux ultrafins avec un bon contrôle de la conduction électrique, mais leur intégration à l’échelle industrielle reste un défi.

En quoi consiste l’intégration “damascène” dans les transistors 2D ?

Elle permet de former des contacts métalliques supérieurs en toute compatibilité avec la fabrication avancée, en enrobant le métal dans une structure en “tranchée” sans endommager le canal 2D, étape essentielle pour rendre ces dispositifs viables à grande échelle.

source : community.intel