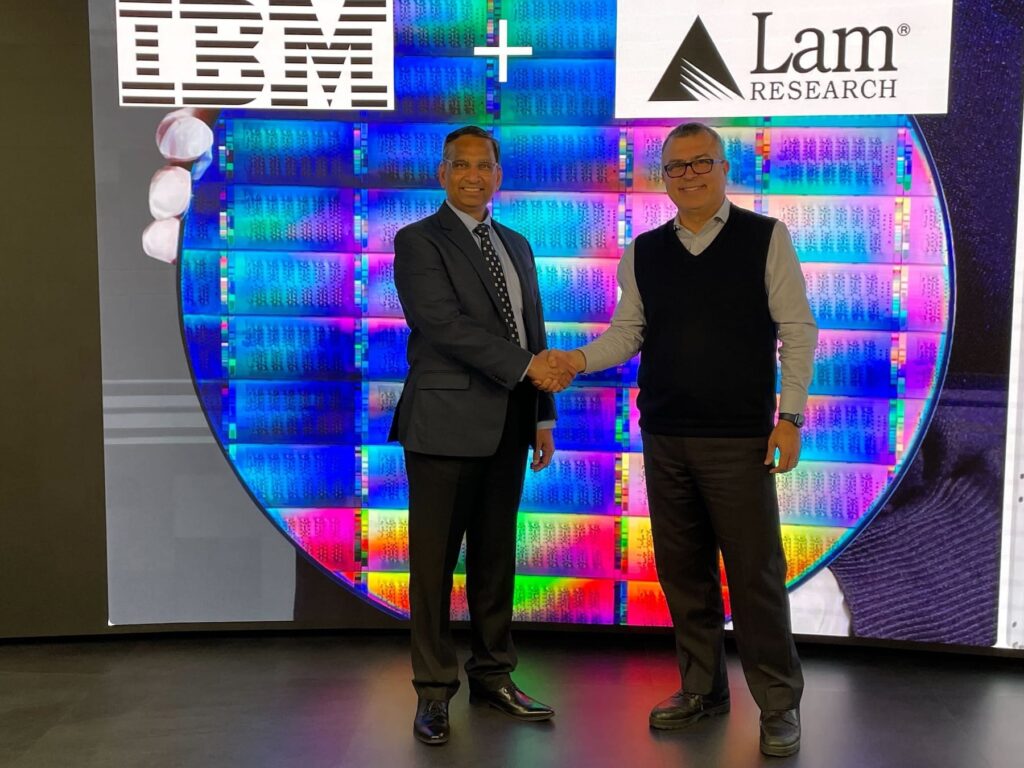

IBM et Lam Research ont annoncé une nouvelle collaboration de cinq ans dont l’objectif vise directement le futur de l’industrie des semi-conducteurs : développer de nouveaux matériaux, processus de fabrication et techniques de lithographie High NA EUV permettant de continuer à réduire l’échelle des puces logiques en dessous du nœud de 1 nanomètre. Cette annonce ne signifie pas que des puces sub-1 nm seront commercialisées à court terme, mais elle confirme l’ambition des deux entreprises de se positionner dans l’une des courses technologiques les plus complexes et déterminantes de la prochaine décennie.

Cette alliance s’appuie aussi sur une relation préalable significative dans le secteur. IBM et Lam rappellent qu’ils collaborent depuis plus d’une décennie sur des technologies de fabrication avancées, ayant déjà contribué à des avancées majeures telles que les processus en 7 nm, les architectures nanosheets et les progrès en lithographie EUV. En 2021, IBM a présenté son premier chip en 2 nm, une démonstration technologique qui a renforcé son rôle de référent dans la recherche sur les semi-conducteurs, même si elle ne produit pas en masse de chips comme une fonderie à l’image de TSMC ou Samsung.

Une démarche de recherche, non un produit immédiat

Ce qu’il faut retenir avant tout, c’est la nature de l’accord. Il ne s’agit pas d’une nouvelle ligne de production commerciale ni d’un prochain nœud prêt pour la fabrication en volume, mais d’un programme de R&D axé sur la conception et la validation de processus complets pour les générations futures de logique avancée. Le travail s’inscrira dans la feuille de route de l’échelle logique d’IBM et se concentrera sur de nouveaux matériaux, des capacités avancées de gravure et de dépôt, ainsi que sur des processus High NA EUV capables de transférer des motifs de taille toujours plus petite sur des couches de dispositifs avec des rendements économiquement viables.

Ce point est crucial, car la progression vers en-dessous de 1 nm ne dépend pas d’une seule amélioration isolée. L’industrie a atteint un stade où la miniaturisation ne consiste plus simplement à réduire tout de manière uniforme, mais à combiner de nouveaux matériaux, des architectures tridimensionnelles, des techniques de patterning de plus en plus fines, tout en maitrisant de façon extrême les défauts, la variabilité et la consommation d’énergie. Lam souligne dans son communiqué que cette démarche est liée à une nouvelle ère de scalabilité 3D, où matériaux, procédés et lithographie doivent fonctionner comme un système intégré de haute densité bien plus avancé qu’auparavant.

Le rôle de la lithographie High NA EUV

Un des éléments clés de cette collaboration est la mise en avant de la lithographie High NA EUV. ASML, le fournisseur principal de cette technologie, explique que ses systèmes de nouvelle génération EXE augmentent l’ouverture numérique de 0,33 à 0,55, améliorant la résolution et permettant d’imprimer des fonctionnalités nettement plus petites avec moins de techniques complexes de multi-patterning. L’EXE:5000, selon ASML, peut atteindre une résolution de 8 nm et produire des éléments 1,7 fois plus petits que ceux possibles avec la version précédente de EUV, contribuant ainsi à augmenter significativement la densité des transistors.

Pour IBM et Lam, ces avancées en lithographie ne suffisent pas à elles seules. C’est pourquoi l’accord inclut aussi le développement de processus pour les interconnexions et des architectures futures comme nanosheets, nanostacks, et la gestion de puissance par l’arrière du chip (backside power delivery). Ce dernier point est particulièrement stratégique, car l’approvisionnement en énergie par la face arrière du puce devient une technique prometteuse pour continuer à faire évoluer performances et efficience tout en conservant un design frontal simplifié. Il ne s’agit donc pas uniquement de créer des structures plus petites, mais de faire en sorte que l’ensemble du transistor et son réseau électrique restent fabriquables et performants en production.

Albany NanoTech et les outils impliqués

La recherche s’appuiera sur les capacités d’IBM au sein du complexe Albany NanoTech, intégré dans l’écosystème de NY CREATES, dans l’État de New York. Ce lieu, depuis des années, est un pôle de collaboration entre acteurs majeurs du secteur. Il réunira ces capacités de recherche avec des outils et plateformes de Lam, comme Aether pour le dry resist, Kiyo et Akara pour la gravure, Striker et ALTUS Halo pour la déposition, ainsi que divers procédés d’assemblage avancé. NY CREATES a également souligné publiquement l’importance de cette collaboration pour son campus, consolidant Albany comme un centre majeur de recherche appliquée en semi-conducteurs aux États-Unis.

La participation d’Aether dans cet accord n’est pas un détail anodin. Lam défend depuis longtemps que sa technologie de dry resist peut aider à dépasser des limitations critiques dans les nœuds avancés, telles que la défectivité, le collapse des motifs ou la difficulté à maintenir la précision à mesure que les pitches se réduisent. Déjà adoptée comme outil de référence par un grand fabricant de mémoire pour les processus DRAM avancés, Aether pourrait, selon Lam, jouer un rôle clé dans la fabrication de dispositifs logiques en 2 nm et en dessous.

Implications pour l’industrie

Ce partenariat illustre une orientation stratégique claire. Avec la demande croissante pour des puces destinées à l’Intelligence Artificielle, le cloud et le calcul haute performance, la pression sur le rythme d’évolution technologique s’intensifie. Si IBM ne produit pas en masse de chips logiques avancés aujourd’hui, son rôle de laboratoire et de laboratoire d’idées reste crucial, car ses innovations peuvent influencer la filière industrielle. De leur côté, Lam a besoin que l’industrie continue à évoluer vers des nœuds plus complexes, pour soutenir une demande de technologies de patterning, gravure et dépôt de plus en plus sophistiquées. Cette alliance souligne que la prochaine grande étape du secteur des semi-conducteurs ne sera pas le fruit d’un seul outil ou matériau, mais bien la conséquence de chaînes de procédés intégrés, co-développés depuis la recherche.

Elle envoie aussi un message implicite à l’écosystème : la lithographie High NA EUV ne relève plus de la simple promesse, mais entre dans une phase concrète. ASML annonce que cette nouvelle génération de systèmes est prête à ouvrir un nouveau chapitre dans la fabrication de pointe, et de nombreux acteurs ont déjà commencé à déployer leurs premières machines commerciales. Toutefois, la transition entre la disponibilité des équipements et la mise en œuvre de processus stables, efficaces et performants demeure un défi. C’est précisément ce que vise cet accord entre IBM et Lam : transformer une promesse de laboratoire en une technologie industrielle viable, étape essentielle pour franchir les prochaines frontières.

Ce mouvement ne doit pas être perçu comme l’arrivée imminente de “puces sub-1 nm”, mais plutôt comme une étape sérieuse pour préparer le terrain. La course à la miniaturisation n’est plus simplement une question de réduction, mais exige des collaborations accrues, et la maîtrise conjointe de la lithographie, de la chimie, des matériaux, de l’intégration 3D et des architectures électriques innovantes. IBM et Lam veulent prendre part à cette évolution dès ses premiers jalons. Bien que le marché devra patienter plusieurs années avant de voir ces avancées se traduire en produits commerciaux, l’orientation est déjà claire : le prochain saut pour le secteur des semi-conducteurs se joue aujourd’hui dans les laboratoires, sur des outils de procédé et dans des lignes pilote, comme celles d’Albany.

Questions fréquentes

Que viennent d’annoncer précisément IBM et Lam Research ?

Ils ont signé un accord de collaboration de cinq ans pour la recherche sur les matériaux, processus de fabrication et techniques de lithographie High NA EUV dédiés à continuer la miniaturisation des puces logiques en dessous de 1 nm. Il ne s’agit pas d’un lancement commercial, mais d’un programme de R&D axé sur la validation des processus.

Qu’est-ce que la lithographie High NA EUV et pourquoi est-ce stratégique ?

High NA EUV désigne la nouvelle génération de lithographie ultraviolette extrême avec une ouverture numérique de 0,55. Selon ASML, cette technologie permet une meilleure résolution que l’EUV précédent, facilitant l’impression de caractéristiques toujours plus petites avec un patterning moins complexe, un enjeu clé pour les futurs nœuds logiques.

Quand pourrait-on voir des puces sub-1 nm sur le marché ?

Aucune date précise n’a été communiquée. Le partenariat concerne la recherche et la validation de processus, ce qui signifie que la production commerciale de tels nœuds reste encore à plusieurs années.

Quel rôle joue Albany NanoTech dans cette collaboration ?

Le projet repose sur l’expertise de IBM au sein du complexe Albany NanoTech, intégré à NY CREATES, où seront développés et validés les processus pour les futures générations de dispositifs logiques.

via : LAM Research